Design av strømforsyninger:

Kan du optimalisere effektiviteten til en svitsjet strømforsyning?

Svar: Selvfølgelig – Effektiviteten kan optimaliseres ved å minimere hot loop PCB ESR (Equivalent Series Resistance) og ESL (Equivalent Series Inductance).

Denne artikkelen er 2 år eller eldre

For kraftomformere kan et mønsterkortlayout med “varme sløyfer” (hot loops) med minimum parasittiske parametere forbedre strømeffektiviteten, senke spenningsringing og redusere elektromagnetisk interferens (EMI).

Denne artikkelen diskuterer optimalisering av design for hot loop-layout ved å minimere mønsterkort- (PCB) ekvivalente seriemotstander (ESR) og ekvivalente serieinduktanser (ESL).

Artikkelen undersøker og sammenligner forskjellige påvirkningsfaktorer,

inkludert posisjonering av avkoplingskondensator, kraft-FET-størrelser og

-posisjoner, og via-plasseringer. Eksperimenter utføres for å verifisere

analysen, og effektive metoder for å minimere PCB ESR og ESL er oppsummert.

Hot Loop og mønsterkortutlegg, parasittiske parametre

Hot Loop for en svitsjet kraftomformer er definert som den kritiske høyfrekvente (HF) vekselstrømsløyfen dannet av HF-kondensatoren og tilstøtende effekt-FET-er. Dette er den mest kritiske delen av krafttrinnet i mønsterkort-utlegget fordi den inneholder høy dv/dt- og di/dt-støy. Et dårlig utformet hot loop-utlegg lider av -parasittiske parametere, inkludert ESL, ESR og ekvivalent parallell kapasitans (EPC), som har en betydelig innvirkning på effektomformerens effektivitet, svitsje- og EMI-ytelse.

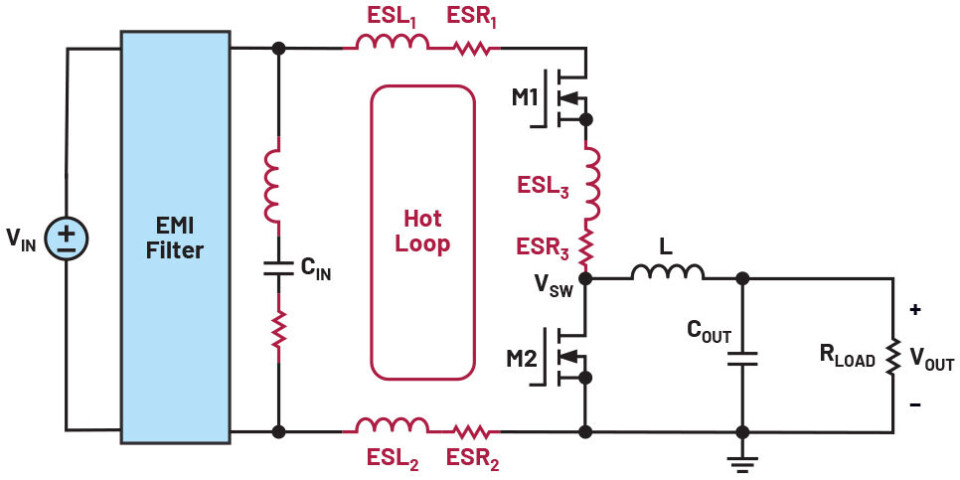

Figur 1 viser en synkron buck step-down DC-til-DC-omformer. Hot Loop dannes av MOSFET-ene M1 og M2 og avkoplingskondensatoren CIN. Svitsjingen av M1 og M2 forårsaker HF di/dt og dv/dt støy. CIN gir en lavimpedanse bane for å omgå HF-støyen. Imidlertid vil man i Hot Loopen ha parasittisk impedans (ESR, ESL) i komponentenes pakker og langs PCB-sporene. Den høye di/dt-støyen gjennom serie induktansene forårsaker dessuten HF-ringing, noe som resulterer i EMI. Energien som er lagret i ESL spres på ESR, noe som fører til ekstra strømtap. Derfor bør ESRs og ESLs i Hot Loop minimeres for å redusere HF-ringingen og forbedre effektiviteten.

En nøyaktig modellering av hot loop ESRs og ESLs hjelper til med å forutsi svitsjeytelsen og forbedre hot loop designet. Både mønsterkortsporene og komponentenes pakker bidrar til de totale parasittiske parametrene i loopen. Denne artikkelen fokuserer hovedsakelig på design av PCB-layout. Det finnes verktøy for å trekke ut parasittiske parametere fra PCB designet, som for eksempel Ansys Q3D, FastHenry/FastCap, StarRC, etc. Kommersielle verktøy som Ansys Q3D gir en nøyaktig simulering, men er vanligvis dyre. FastHenry/FastCap er et gratis verktøy basert på numerisk modellering av partielle elementekvivalente kretser (PEEC)1 og kan gi fleksibel simulering gjennom programmering for å utforske forskjellige layoutdesign. Ytterligere koding er imidlertid nødvendig. Effektiviteten og nøyaktigheten for den parasittiske parameterekstraksjonen i FastHenry/FastCap er verifisert og sammenlignet med Ansys Q3D med konsistente resultater.2,3 I denne artikkelen brukes FastHenry som et kostnadseffektivt verktøy for å trekke ut PCB ESRer og ESLer.

Hot Loop PCB ESR og ESL vs. posisjonering av avkoplingskondensator

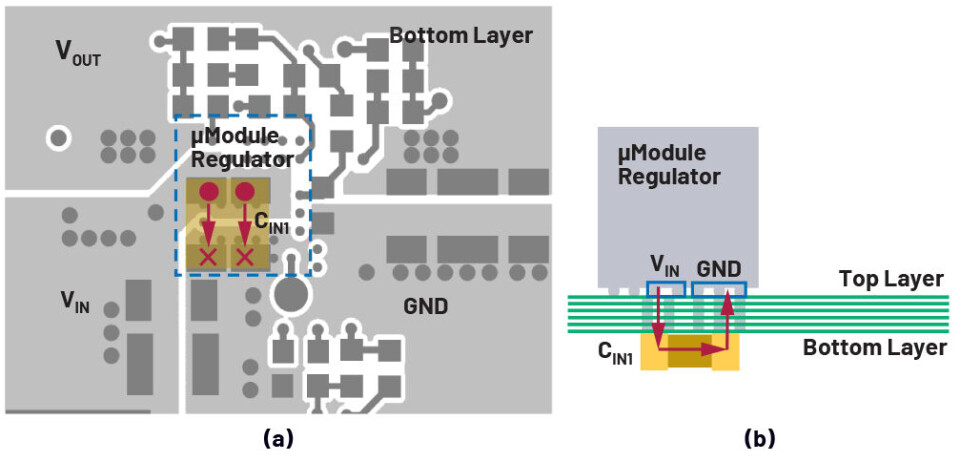

I denne delen blir virkningene av CIN-posisjonen undersøkt basert på ADIs LTM4638 µModule®-regulator demokort DC2665A-B. LTM4638 er en integrert 20 VIN, 15 A step-down buck-konverter modul i en liten 6,25 mm × 6,25 mm × 5,02 mm BGA-pakke. Den gir høy effekttetthet, rask transientrespons og høy effektivitet. Modulen integrerer en liten HF-keramisk CIN, selv om den ikke er stor nok, noe som er begrenset av modulpakkestørrelsen. Figurene 2 til 4 illustrerer tre forskjellige Hot Loops på demokortet, hvor det i tillegg benyttes en ekstra ekstern CIN. Den første er den vertikale Hot Loop 1 (Figur 2), der CIN1 er plassert på bunnlaget like under μModule-regulatoren. µModule VIN og GND BGA pinnene er koblet til CIN1 direkte gjennom viaene. Disse tilkoblingene gir den korteste hot loop-banen på demokortet.

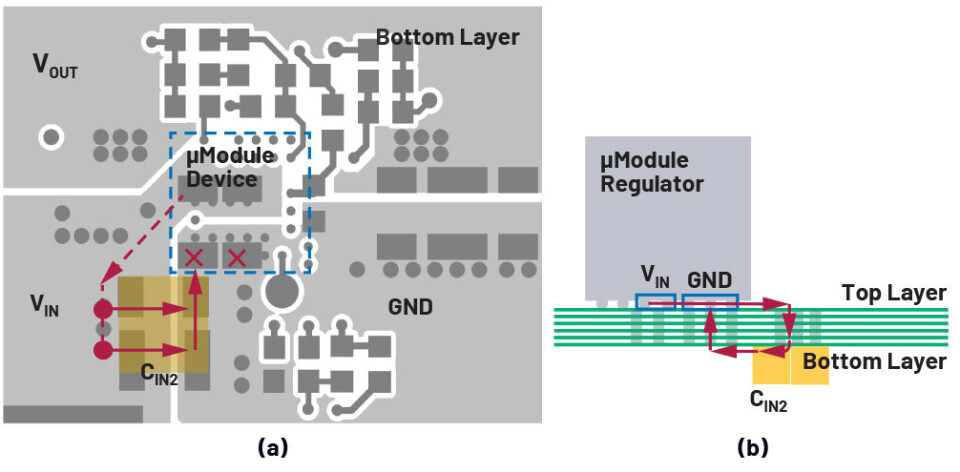

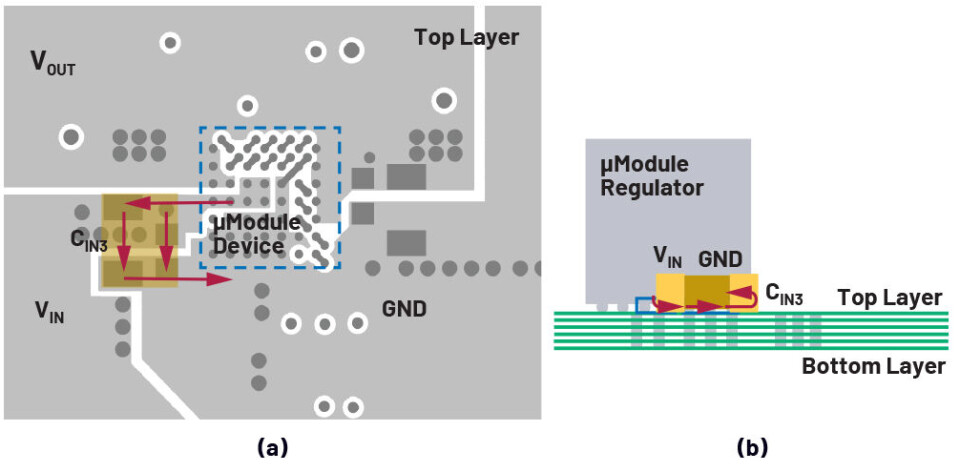

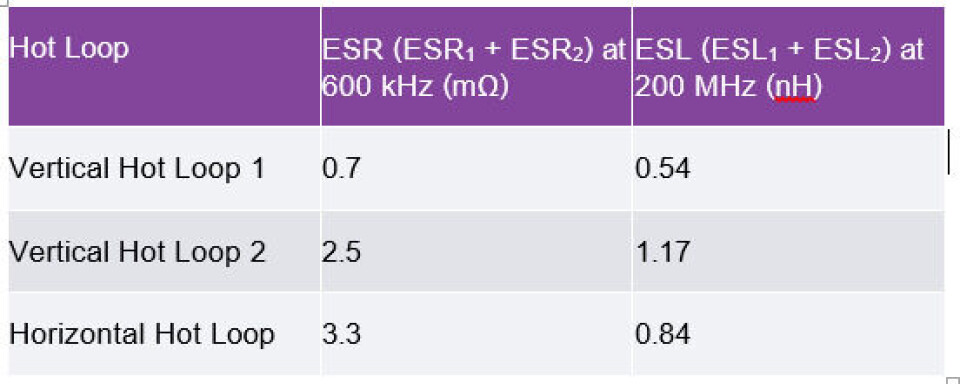

Den andre varmesløyfen er den vertikale Hot Loop 2 (Figur 3), hvor CIN2 fortsatt er plassert på bunnlaget, men flyttet til området noe til siden for μModule-regulatoren. Som et resultat blir det lagt til et ekstra PCB-spor til hot loopen og vi vil få større ESL og ESR sammenlignet med vertikal Hot Loop 1. Det tredje alternativet for hot loop er horisontal hot loop (Figur 4), hvor CIN3 er plassert på topplaget nær μModule-regulatoren. µModule VIN og GND pinnene er koblet til CIN3 gjennom topplag-kobberet uten å gå gjennom vias. Ikke desto mindre er VIN-kobberbredden på det øverste laget begrenset av den andre pin-utgangen, noe som resulterer i en økt sløyfeimpedans sammenlignet med den for vertikal Hot Loop 1. Tabell 1 sammenligner de ekstraherte PCB-ESR og ESL cerdiene til hot loop ved bruk av FastHenry. Som forventet har den vertikale Hot Loop 1 den laveste PCB ESR og ESL.

Tabell 1. Ekstraherte PCB ESRer og ESLer i forskjellige Hot Loops ved å bruke FastHenry

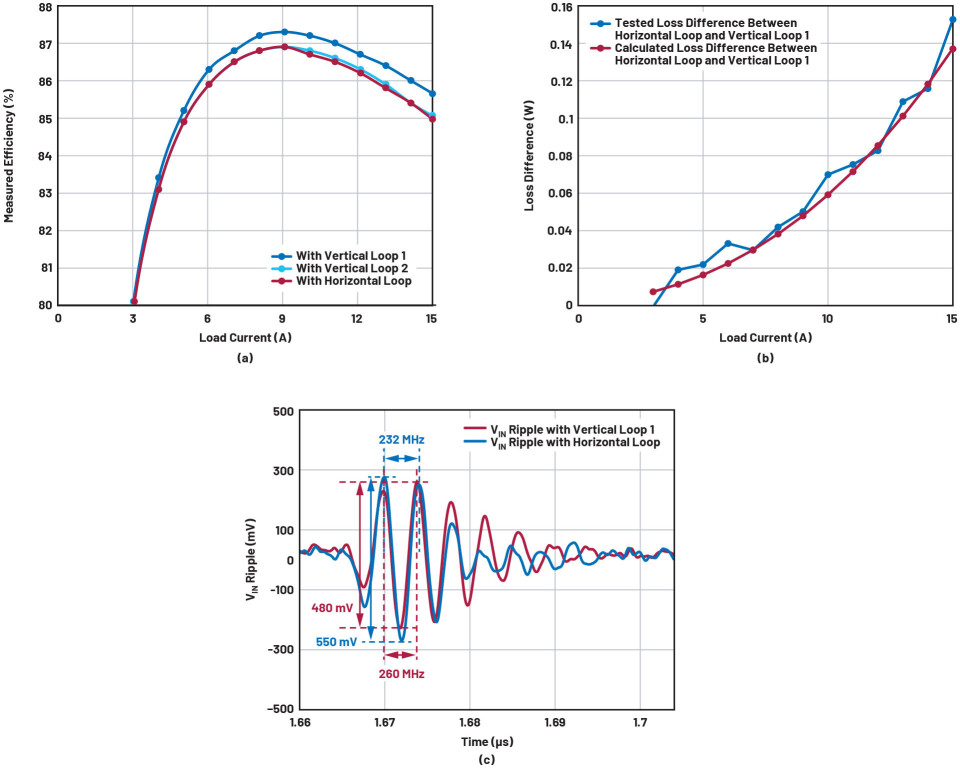

For å eksperimentelt verifisere ESR-ene og ESL-ene i forskjellige varmesløyfer, testes demokortets effektivitet og VIN AC-rippel ved 12 V til 1 V CCM-drift. Teoretisk sett fører en lavere ESR til høyere effektivitet, og mindre ESL resulterer i høyere VSW-ringefrekvens og lavere VIN-rippelstørrelse. Figur 5a viser målt effektivitet. Den vertikale Hot Loop 1 gir den høyeste effektiviteten som tilsvarer laveste ESR. Forskejllen i tap mellom den horisontale varmesløyfen og den vertikale varmesløyfen 1 er også beregnet basert på de ekstraherte ESR-ene. Resultatet er i samsvar med testresultatet som vist i figur 5b. VIN HF-rippel-kurveformene i figur 5c er testet der den krysser CIN. Den horisontale varmesløyfen har en høyere VIN-rippelstørrelse og en lavere ringefrekvens, og validerer dermed den høyere loop ESL sammenlignet med den vertikale Hot Loop 1. På grunn av høyere loop ESR, dempes VIN-rippelen i den horisontale varmesløyfen raskere enn i den vertikale Hot Loop 1. Videre vil en lavere VIN-rippel redusere EMI og dermed tillate en mindre EMI-filterstørrelse.

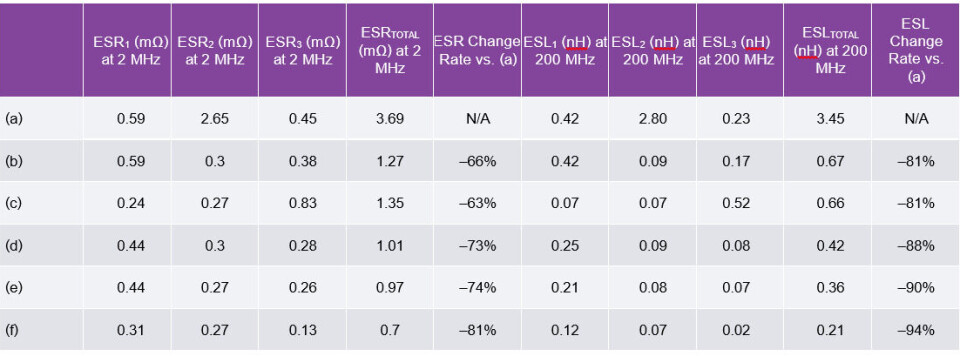

Tabell 2. Ekstrahert Hot Loop PCB ESR og ESL med forskjellige former og posisjoner i FastHenry

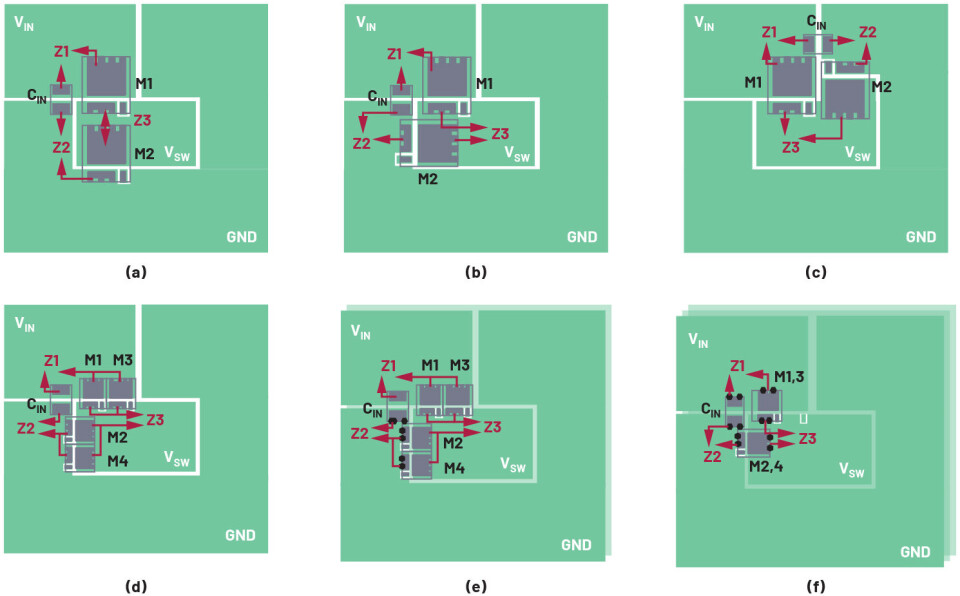

Hot Loop PCB ESR og ESL vs. MOSFETens størrelse og plassering

For et diskret design har plasseringen og pakkestørrelsen til power-FET-er også en betydelig innvirkning på hot loop ESRog ESL. En typisk halvbro hot loop med power-FET-er M1 og M2 og en avkoplingskondensator CIN er modellert og undersøkt i denne delen. Som illustrert i figur 6, sammenlignes populære power FET-pakkestørrelser og plasseringsposisjoner. Tabell 2 viser de ekstraherte ESR-ene og ESL-ene i hvert tilfelle.

Sakene (a) til (c) presenterer tre populære power FET-plasseringer med 5 mm × 6 mm MOSFET-er. Den fysiske lengden på Hot Loop bestemmer den parasittiske impedansen. Derfor resulterer både 90˚ rotering i tilfelle (b) og 180˚ rotasjon i tilfelle (c) i 60 % ESR-reduksjon og 80 % ESL-reduksjon på grunn av de kortere sløyfebanene sammenlignet med de i tilfelle (a). Siden en 90˚ rotasjon gir en betydelig fordel, blir flere tilfeller undersøkt basert på (b) for å redusere loop ESR og ESL ytterligere. I tilfelle (d) erstattes en 5 mm × 6 mm MOSFET med to 3,3 mm × 3,3 mm MOSFET-er i parallell. Sløyfelengden er ytterligere forkortet takket være mindre MOSFET fotavtrykk, noe som fører til 7 % reduksjon i impedans. I tilfelle (e), når et jordlag er plassert under Hot Loop laget, reduseres varmesløyfens ESR og ESL ytterligere med 2 % sammenlignet med tilfelle (d). Årsaken er at det genereres virvelstrøm på jordlaget, som induserer det motsatte magnetfeltet og tilsvarende reduserer loop impedansen. I tilfelle (f) er et annet Hot Loop lag konstruert som bunnlag. Hvis to parallelle MOSFET-er er symmetrisk plassert på topplaget og bunnlaget, og koblet sammen gjennom vias, er hot loop PCB ESR og ESL-reduksjonen mer åpenbar på grunn av den parallelle impedansen. Derfor fører mindre komponenter med symmetrisk 90˚ eller 180˚ rotering på topp- og bunnlag til den laveste PCB ESR og ESL.

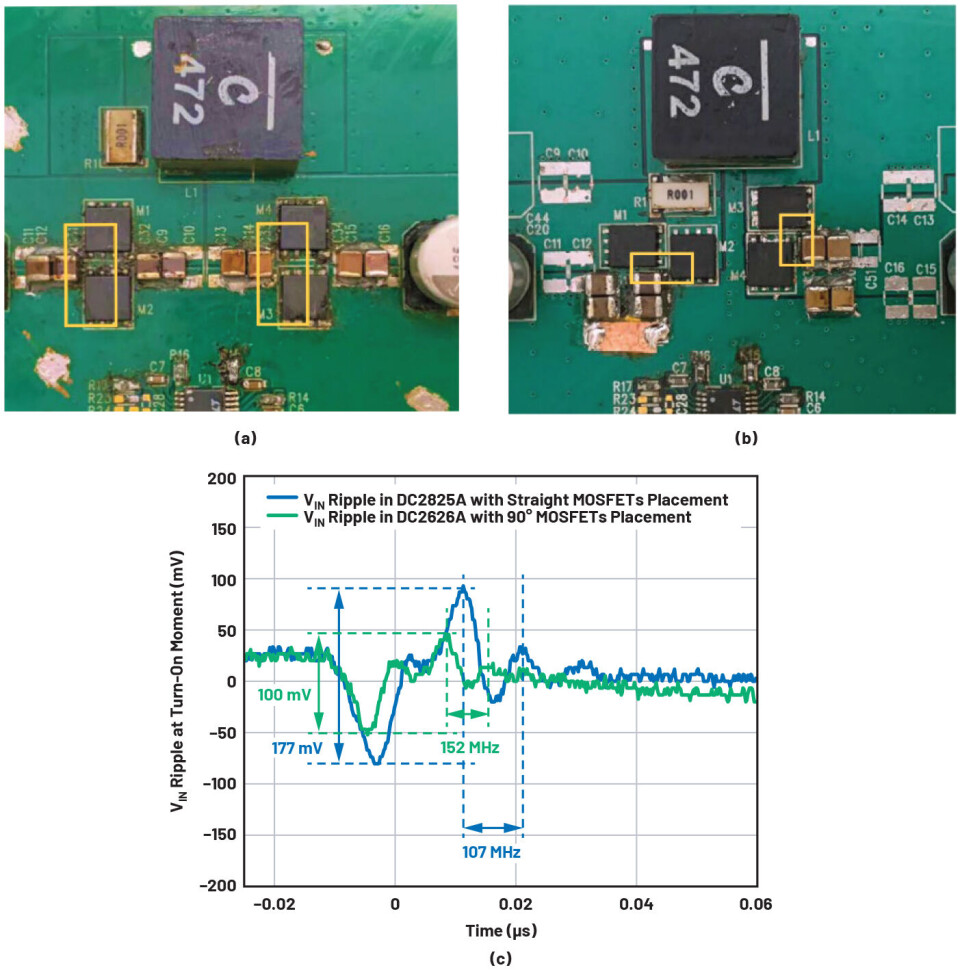

For å eksperimentelt verifisere virkningen av MOSFET-plasseringen, brukes ADIs høyeffektive, 4-svitsj synkron buck-boost-kontroller-demokort LT8390/DC2825A og LT8392/DC2626A.4 Som vist i figur 7a og figur 7b, har DC2825A en rett MOSFET-plassering og DC2626A har en MOSFET-plassering på 90˚. For å gjøre en rettferdig sammenligning er de to demokortene konfigurert med de samme MOSFET og avkoplingskondensatorer, og testet ved 36 V til 12 V/10 A, 300 kHz step-down drift. Figur 7c viser den testede VIN AC-rippelen under M1-startmomentet. Med 90˚-form MOSFET-plasseringen, har VIN-rippelen lavere styrke og høyere resonansfrekvens, og bekrefter derfor mindre PCB ESL på grunn av en kortere hot loop-bane. På den andre siden , på grunn av den lengre varmesløyfen og høyere ESL, resulterer den rette MOSFET-plasseringen i mye høyere VIN-rippel og langsommere resonansfrekvens. En høyere inngangsspenningsrippel forårsaker også et mer alvorlig EMI-stråing i henhold til EMI-testresultatene i studien av Cho og Szolusha.4

Hot Loop PCB ESR og ESL vs. Via-plassering

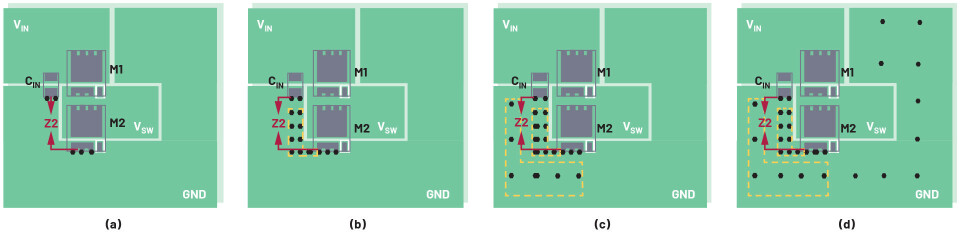

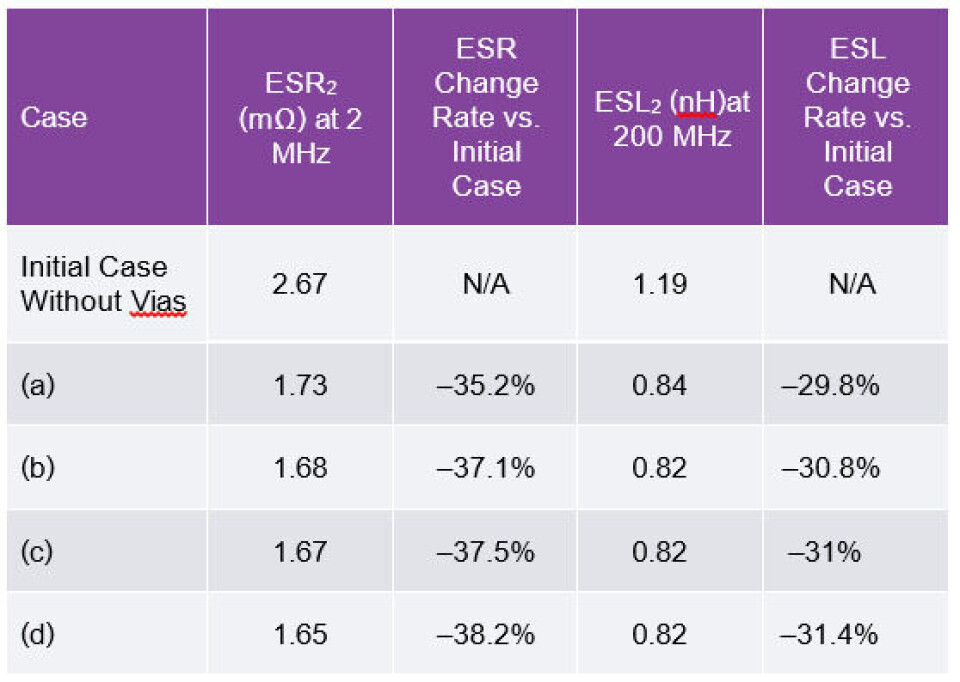

Via-plassering i hot loop har også en kritisk innvirkning på loop ESR og ESL. Som vist i figur 8, modelleres den varme sløyfen med en to-lags PCB-struktur og plassering av rett power-FET. FET-ene er plassert på topplaget og det andre laget er et jordplan. Den parasittiske impedansen Z2 mellom CIN GND-puten og M2-kildeputen er en del av hot loopen og brukes som eksempel. Z2 er hentet fra FastHenry. Tabell 3 oppsummerer og sammenligner de simulerte ESR2 og ESL2 med forskjellige via-plasseringer.

Generelt sett reduserer det å legge til flere vias den parasittiske PCB-impedansen. Reduksjonen av ESR2 og ESL2 er imidlertid ikke lineært proporsjonal med antall vias. Viaene nær terminalputene gir den mest åpenbare reduksjonen i PCB ESR og ESL. Derfor, for design av hot loop layout, må flere kritiske vias plasseres nær pad’ene til CIN- og MOSFET-er for å minimere HF-sløyfeimpedansen.

Tabell 3. Ekstrahert Hot Loop PCB ESR2 og ESL2 med forskjellige Via-plasseringer

Konklusjon

Reduksjonen av en hot loops parasittiske parametere kan bidra til å forbedre strømeffektiviteten, lavere spenningsringing og redusere EMI. For å minimere PCB-parasitiske parametere, ble design med varmesløyfe-layout med forskjellige posisjoner for avkoplingskondensatorer, MOSFET-størrelser og -posisjoner og via-plasseringer studert og sammenlignet. En kortere hot loop-bane, mindre størrelse MOSFET-er, symmetrisk 90˚-form og 180˚-form MOSFET-plasseringer, og vias nær nøkkelkomponentene bidrar til den laveste hot loop PCB ESR og ESL.

Referanser

1Mattan Kamon, Michael Tsuk, and Jacob White. “FASTHENRY: A Multipole-Accelerated 3-D Inductance Extraction Program.” IEEE Transactions on Microwave Theory and Techniques, Vol. 42, 1994.

2Andreas Musing, Jonas Ekman, and Johann W. Kolar. “Efficient Calculation of Non-Orthogonal Partial Elements for the PEEC Method.” IEEE Transactions on Magnetics, Vol. 45, 2009.

3Ren Ren, Zhou Dong, and Fei Fred Wang. “Bridging Gaps in Paper Design Considering Impacts of Switching Speed and Power-Loop Layout.” IEEE, 2020.

4Yonghwan Cho and Keith Szolusha. “4-Switch Buck-Boost Controller Layout for Low Emissions—Single Hot Loop vs. Dual Hot Loop.” Analog Dialogue, Vol. 55, July 2021.

5Henry J. Zhang. “PCB Layout Consideration for Non-Isolated Switching Power Supplies.” Analog Devices, Inc., 2012.

6Christian Kueck. “Power Supply Layout and EMI.” Analog Devices, Inc., 2012.