Sponset artikkel

Hvordan designe og verifisere et digitalt filter ved å bruke MATLAB med Eclypse Z7 som «FPGA-in-the-loop»

Digitale filtre som kjører på innebygd maskinvare eller FPGA-er vil mest sannsynlig bruke fastpunkt-aritmetikk. Effektene av kvantisering må sjekkes under utvikling, fortrinnsvis med «hardware-in-the-loop». Ved å bruke MATLAB og et Eclypse Z7 FPGA-kort med Zmods for datakonvertering, er det enkelt.

Denne artikkelen er 2 år eller eldre

Når vi hører uttrykket «programvare for engineering», tenker de fleste av oss ingeniører umiddelbart på MATLAB. Det er få områder innen engineering som MATLAB ikke tilbyr en pakke for, og digital signalbehandling og FPGA-design er definitivt ikke blant dem. MATLABs Signal Processing Toolbox gir utviklere alle funksjonene de trenger for å lage et filter eller et hvilket som helst signalbehandlingssystem. Fixed-Point Designer kvantisere dataene og hjelper til med å implementere fastpunkt- og flytpunktalgoritmer i prosesseringssystemet og sjekke effektene på det digitale systemet. Og pakker som HDL Coder, HDL Verifier og FPGA Data Capture lar dem teste designet på en ekte FPGA som hardware-in-the-loop og overføre det resulterende systemet til FPGA-kortet. På denne måten blir det mindre komplekst å lage et signalbehandlingssystem.

Anta at vi ønsker å designe et båndpassfilter for et kommunikasjonssystem for å trekke ut et bestemt signal fra en linje som bruker frekvensdelingsmultipleksing. Denne teknikken er brukt lenge, for eksempel for å sende forskjellige radiostasjoner over samme datalinje, over luft. Et annet tilfelle er kraftlinjekommunikasjon (PLC), hvor vi kan overføre strøm ved nettfrekvenser på 50Hz eller 60Hz, og data ved frekvenser på flere hundre kilohertz.

Når filteret er designet, ønsker vi å kjøre det på ekte maskinvare. Dette maskinvaresystemet kan for eksempel omfatte et Eclypse Z7 Zynq-7000 SoC (System on Chip) FPGA-kort fra Digilent med én Zmod Scope 1410 2-kanals 14-bits oscilloskopmodul og én Zmod AWG 1411 2-kanals 14-bits vilkårlig bølgeformgeneratormodul – begge fra Digilent – montert på toppen. Ved hjelp av analog-til-digital-omformeren (ADC) til Zmod Scope 1410 kan vi digitalisere linjesignalet og vi kan sende ut både det samplede og det filtrerte signalet gjennom digital-til-analog-omformeren (DAC) på Zmod AWG, mens du kjører selve filteret på Zynq-7000.

Utforme filteret og ta vare på kvantisering

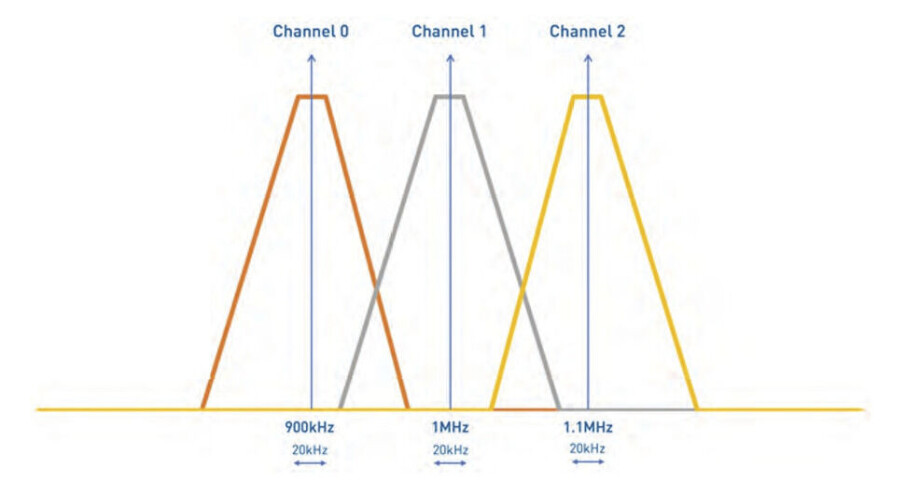

Figur 2 viser frekvensspekteret til overføringslinjen vår. Hver kanal har en båndbredde på 20 kHz, og kanalene har en avstand på 100 kHz. Vår interessekanal er kanal 1, og vi vil designe vårt båndpassfilter for å unngå forstyrrelser fra de andre kanalene. For å gjøre dette må vi sørge for en demping på minst -60dB ved båndbredden til de andre kanalene. For å få denne karakteristikken bør filteret vårt ha et passbånd mellom 990kHz og 1010kHz, et stoppbånd md lavere frekvens som strekker seg fra 0Hz til 910kHz, og et stoppbånd med høyere frekvens som starter på 1090kHz.

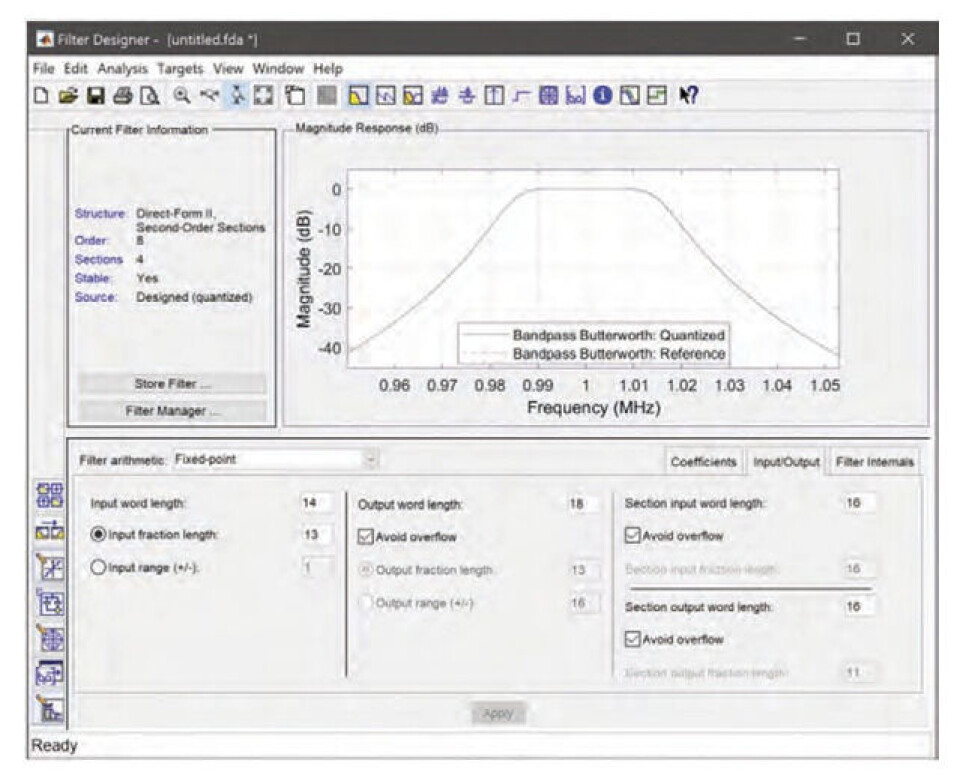

Ved hjelp av Filter Designer-verktøyet fra MATLAB kan vi konfigurere alle disse aspektene ved vårt digitale filter. For vårt eksempel bruker vi et IIR (Infinite Impulse Response) Butterworth-filter, fordi det lar oss designe et lavordensfilter med høy demping og det har et ganske flatt passbånd. Samplingsfrekvensen vil bli valgt for å tilfredsstille både maskinvarekravene til våre dataomformere – 105MSPS for AD9648-105 ADC fra Analog Devices på Zmod Scope og 100MSPS for AD9717 DAC, også fra Analog Devices – og Nyquists samplingsteorem. For vårt eksempel er 10MSPS tilstrekkelig.

I tillegg, siden våre dataomformere er 14-bits fastpunktskomponenter, må vi kvantisere dataene til filteret gjennom filterkvantiseringspanelet i «Filter Designer Tool» for å matche ordlengdene, men også på en måte som ikke fører til oppløsningstap. Når vi har skrevet inn alle parametere i filterdesigneren og generert filteret, vil filterdesigneren vise oss DFT (Discrete Fourier Transformation) for filterets respons. Nå kan vi eksportere den til en Simulink-modell, hvor vi kan kjøre en første test og verifisere om den kvantiserte modellen oppfyller de definerte kriteriene. Som simuleringsinngang genererer vi i MATLAB et sumsignal fra de tre ønskede frekvensene.

Bringe maskinvaren inn i sløyfen

Hvis filteret oppfører seg tilfredsstillende, kan vi generere HDL-koden (Hardware Description Language) ved hjelp av HDL-koderen for å teste filteret på Eclypse Z7 FPGA-kortet, etter å ha gjort noen få modifikasjoner av Simulink-modellen slik at vi kan generere HDL-koden for hele systemet.

«HDL Block Properties»-vinduet lar oss konfigurere pipeline-registrene og arkitekturen når det gjelder multiplikatorer som brukes. Vi må velge en av tre forskjellige arkitekturmodeller: en helt parallell, en helt seriell og en delvis seriell arkitektur.

Med den fullstendig parallelle arkitekturen, kan utdatafrekvensen være den samme som klokkefrekvensen, og hver multiplikasjon av filteret vil bruke en DSP-del av FPGA. Den fullstendig serielle implementeringen bruker imidlertid bare én DSP-skive, men utgangsfrekvensen vil reduseres til (klokkehastighet) / (antall multiplikasjoner), noe som sakker ned beregningstiden. Den delvis serielle arkitekturen er endelig i midten, med antall skiver som kan velges. Dette har den ulempen at antallet brukte logiske elementer øker. Siden vi har nok DSP-skiver på Zynq-7000 SoC på Eclypse Z7, er full parallell et godt valg. Som et siste trinn her velger vi HDL-målspråket, enheten som brukes, tilbakestillingen og rapportene som ønskes på siden for HDL-koderegenskaper. Med alle konfigurasjonene utført, kan vi generere HDL-koden for undersystemet vårt.

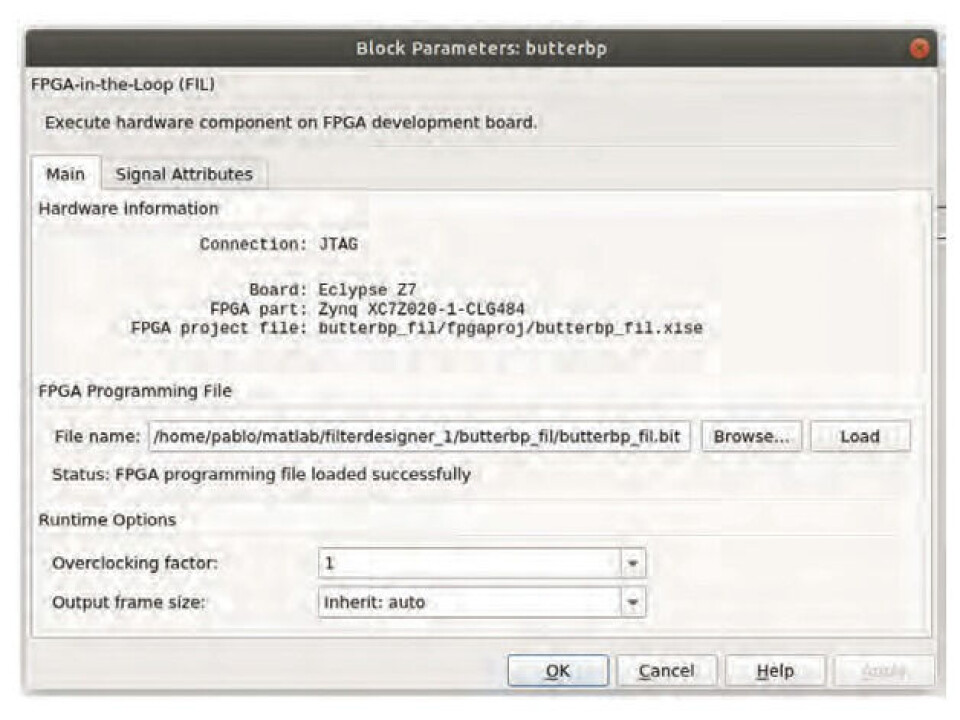

Nå kan vi simulere filteret med FPGA i sløyfen. Dette betyr at filteralgoritmen vil kjøre direkte på FPGA-en og ikke i programvaren på vertsarbeidsstasjonen. Det er her MATLABs FIL (FPGA-in-the-Loop) verktøy kommer inn. Det lar oss, etter å ha laget kortdefinisjonen, koble oss til kortet.

Nå kan vi bygge prosjektet og Vivado, Xilinx’ HDL-syntese- og analyseverktøy, vil åpne i MATLAB-kommandovinduet og syntetisere og implementere FIL-demo-designet. Når Vivado er ferdig med syntesen, vil en Simulink-modell åpnes, som viser den ekstra FIL-blokken. Nå kan vi koble til Eclypse Z7-kortet og laste FIL-modellen inn i FPGA.

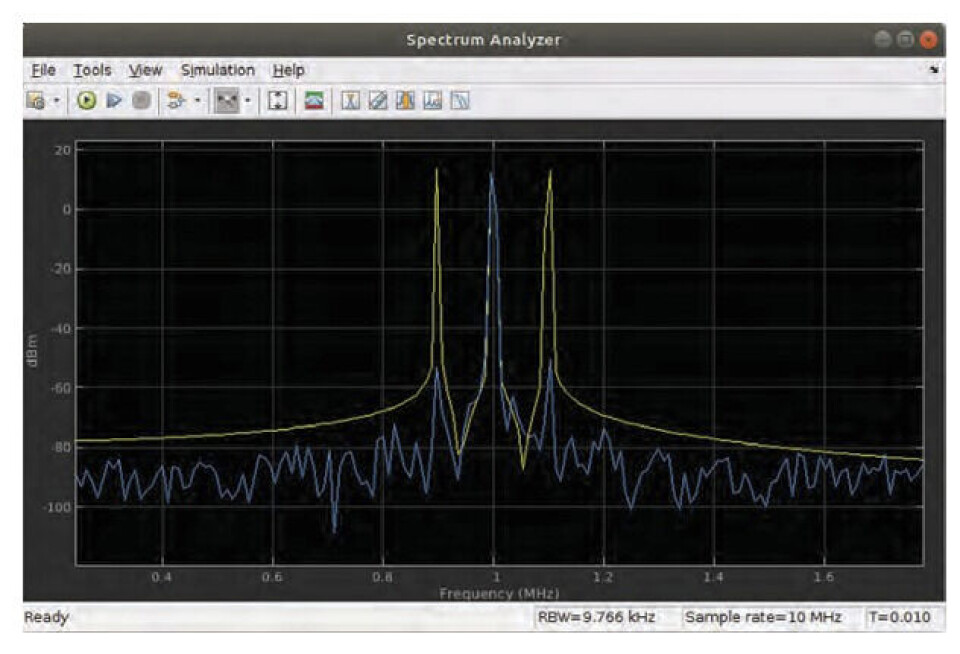

For å simulere signalkilden må tre sinusbølgesignaler som representerer de tre båndene i overføringslinjen legges til, med frekvenser på 900kHz, 1MHz og 1,1MHz. For å bekrefte utdataene trenger vi et spektrumanalyse-vindu. Når simuleringen er ferdig, inneholder utgangen kun 1MHz-signalet.

Bruke datafangst for verifisering

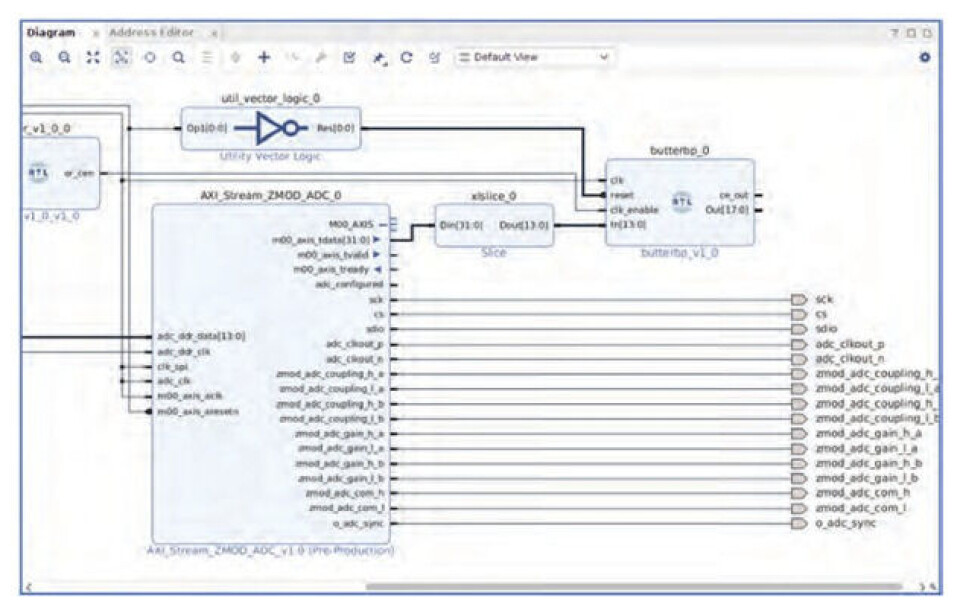

Med filteret testet og verifisert med FPGA-in-the-loop, kan vi lage den endelige applikasjonen, som ikke bare bruker filteret, men også ADC- og DAC-kortene. For dette lager vi et Vivado-prosjekt der vi legger til alle nødvendige blokker, som Zynq-7000, driverne for dataomformerne og klokkegeneratoren.

På Zynq-7000 SoC vil vi ikke bruke prosesseringssystemet, bare den programmerbare logikken (PL). Som klokkekilde vil vi bruke 125MHz-klokken fra Ethernet PHY på Eclypse Z7-kortet, som er koblet til PL. En ekstra klokkeaktiveringsgenerator for å lage filtersamplingsklokken på 10MHz og systemklokken på 100MHz er også nødvendig.

For ADC-kortdriveren vil vi bruke AXI (Advanced eXtensible Interface)-Stream Interface IP. Når vi legger til filteret, må vi ta vare på datastørrelsene, fordi utgangen til AXI-Stream IP er 32 bit bred og inneholder dataene til begge ADC-kanalene. Dataordet som tilsvarer kanal 1 er på de nederste 14 bitene av ordet, så det må trekkes ut.

Tilsvarende gjelder for DAC-driveren, der de øvre utgangsbitene til filteret må forkastes, ved å bruke en Slice-blokk. Vårt eksempelprosjekt bruker begge DAC-kanalene: filterutgangen er koblet til kanal 1 og det originale signalet, som samplet av ADC, er koblet til kanal 2 for verifisering gjennom et oscilloskop.

Når blokkdesignet er fullført, kan vi validere det, lage HDL-innpakningen og generere bitstrømmen. Når designet er syntetisert og implementert, kan vi teste designet på Eclypse Z7-kortet, sammen med en signalgenerator og et oscilloskop. Ved hjelp av en 1MHz sinusbølge kan passbåndet kontrolleres, og med et 910kHz signal, stoppbåndet. Denne bekreftelsen indikerer at alt fungerer som forventet.

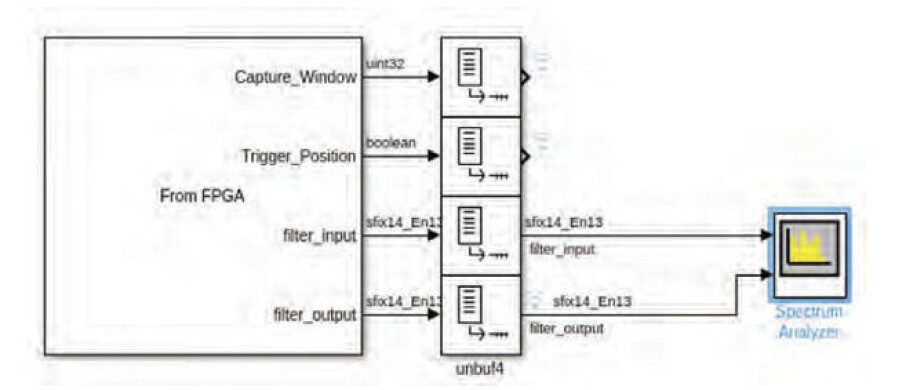

En annen mulighet er å bruke en logikkanalysator, enten en ekstern enhet eller Integrated Logic Analyzer (ILA) fra Xilinx, som kan brukes til å overvåke inn- og utdataene inne i FPGAen og eksportere den til MATLAB. En tredje mulighet er å bruke FPGA Data Capture-funksjonen til MATLAB, som automatisk genererer en IP-blokk som fanger opp sanntidsdata fra FPGA og sender den til MATLAB eller Simulink via JTAG. FPGA Data Capture er en del av HDL Verifier Support Package for Xilinx FPGA-kort.

I vinduet for generering av FPGA-datafangstkomponenter kan filterinngangs- og utgangsportene legges til, og bufferstørrelsen og maksimal sekvensdybde settes. Når det er gjort, vil verktøyet generere HDL IP-kjernen, samt et skript for å starte datafangsten fra MATLABs arbeidsområde, og en Simulink-modell for å fange data fra Simulink. Det siste trinnet er å legge til alle filene til prosjektet og datafangstmodulen til blokkdesignet. Deretter kan vi generere bitstrømmen.

For å teste systemet, må vi lukke maskinvareserveren fra Vivado for å frigjøre JTAG-porten. Noen justeringer av Simulink-datainnsamlingsmodellen, for eksempel å fjerne oscilloskop og erstatte det med spektrumanalysatoren, og konfigurere datatype og format, er også nødvendig.

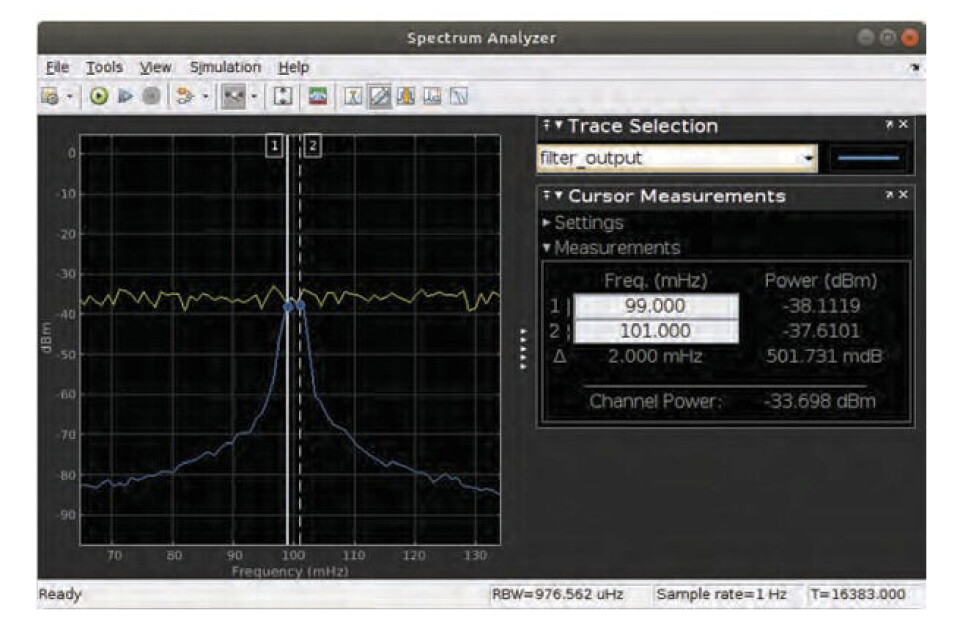

Med hvit støy generert av en ekstern signalgenerator ser vi at filteret fungerer som forventet i frekvensområdet fra 990kHz til 1010kHz uten demping. Det er imidlertid en liten hake: Oppdateringshastigheten til analysatoren er 1Hz i stedet for 10MHz i det virkelige designet.

Dette prosjektet viser at det er mulig å enkelt designe et digitalt filter, sjekke det trinn for trinn, og til slutt verifisere det med et Eclypse Z7 Zinq-7000-kort som hardware-in-the-loop, ved å bruke de forskjellige pakkene til MATLAB og Vivado . En fullstendig trinn-for-trinn-veiledning for dette prosjektet er tilgjengelig her:

Eclypse Z7 er tilgjengelig hos Elfa Distrelec, den autoriserte distributøren i Norge.