Mikroelektronikkprisen:

Standardcellebibliotek for design av digitale kretser med subterskel forsyningsspenninger

Moderne system-on-chips (SoCs) integrerer millioner av enheter på én enkelt chip for å oppnå høy ytelse og energieffektiv operasjon. Ved store teknologiske fremskritt de siste tiårene har energiforbruket blitt betydelig redusert gjennom nedskalering av transistornoden.

Figur 1 oppsummerer minimum svitsjingenergi over tid for større aritmetikkbaserte systemer, hvor det observeres at den eksponentielle reduksjonen gradvis avtar. Det stadig økende behovet for lavere energiforbruk i digitale kretser utfordrer designere til å utvikle nye teknikker på kretsnivå.

Subterskel operasjon

Subterskel operasjon, hvor forsyningsspenningen reduseres under terskelspenningen til transistorene, viser lovende resultater for bruksområder der drift med lave spenninger og lavt effektforbruk er de primære begrensingene. Systemer drevet av energihøstere og lav-effekts IoT noder kan spesielt dra nytte av subterskel operasjon.

Design for subterskel operasjon medfører en rekke nye utfordringer. Dette kommer blant annet av følsomheten for variasjoner i prosess, spenning, og temperatur. I tillegg er nøyaktig modellering av transistorkarakteristikker svært utfordrende i denne regionen. Lavere forsyningsspenninger betyr også mindre marginer mellom hva som kan tolkes som gyldige logiske høye og lave verdier. Derfor vil en designmetodikk som fokuserer på robust operasjon være essensiell.

![Figur 1: Eksperimentell data av minimum svitsjingenergi i digitale enheter brukt i større systemer. Rådata er kompilert fra [1].](https://image.elektronikknett.no/3204715.webp?imageId=3204715&width=960&height=720&format=jpg)

Vårt prosjekt

Standardcellebiblioteket utviklet i vårt prosjekt bruker Schmitt-Trigger (ST) topologier realisert i 130nm silicon- on-insulator (SoI) teknologi for å oppnå robust operasjon ved en nominell forsyningsspenning på 85mV. SoI er en fabrikasjonsteknologi hvor et isolerende lag legges mellom transistoren og substratet for å redusere lekkasjestrømmer og begrense parasittkapasitans, samt kortkanaleffekter.

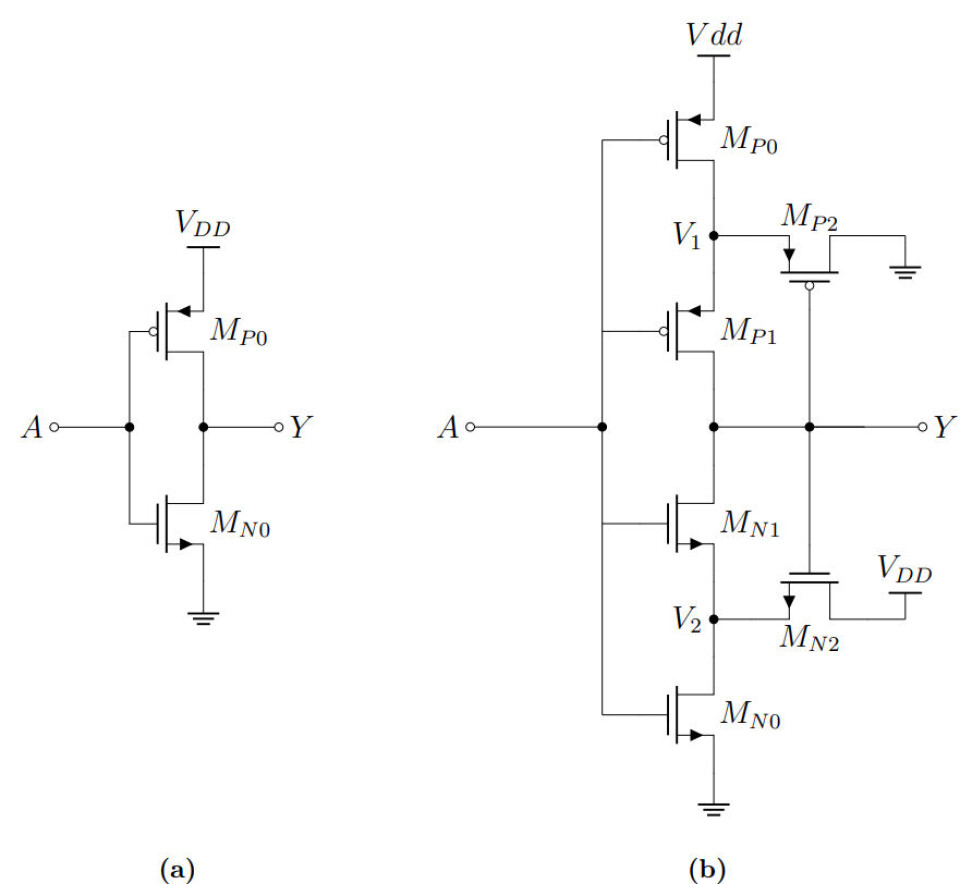

ST baserte logiske porter benytter seg av lekkasjebegrensende prinsipper der transistorene seriekobles. For å illustrere dette prinsippet, vises to versjoner av en inverterende krets under. Figur 2(a) er en konvensjonell CMOS NOT port, mens figur 2(b) er en ekvivalent ST variant.

Hvordan utvikle et subterskel standardcellebibliotek?

Standardcellebiblioteket ble utviklet og evaluert gjennom en iterativ prosess oppsummert i figur 3. Dette inkluderer karakterising av transistorer, design av kombinatoriske og sekvensielle kretser, simulering, utlegg, syntese og verifikasjon. For å ta hensyn til realistiske, ikke-ideelle forhold benyttes Monte Carlo simuleringer med transistor mismatch og prosessvariasjoner.

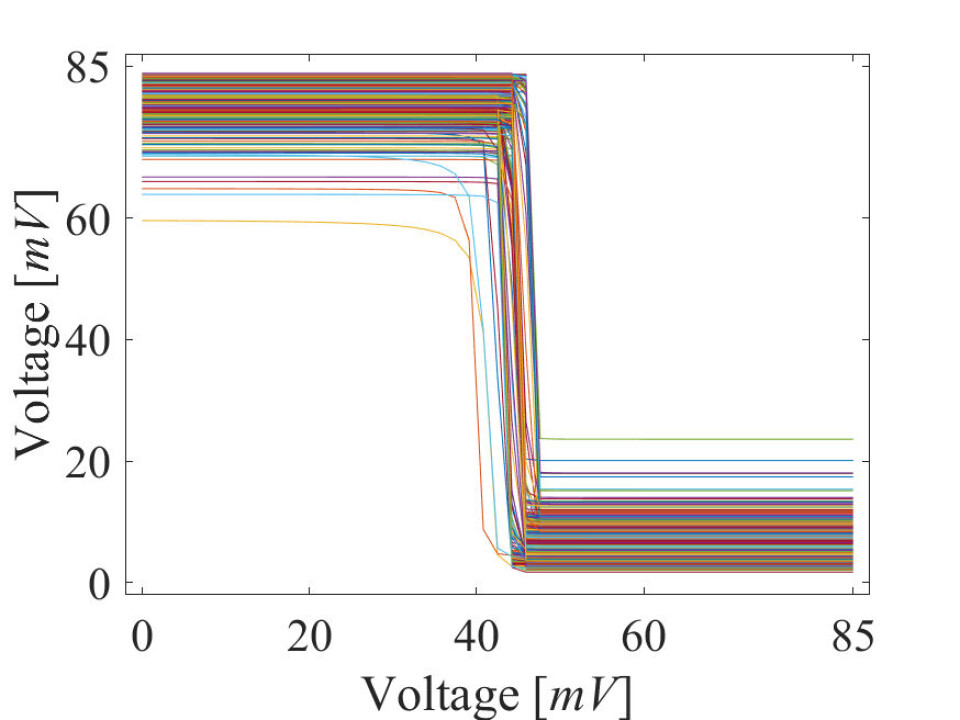

De enkleste logiske portene oppnådde yield over 99.9% ved en nominell spenning på 85mV, målt etter portens evne til å produsere gyldige logiske signaler. Et eksempel på dette vises i figur 4, hvor DC-responsen til en addisjonskrets konstruert av NAND og NOR porter plottes for alle Monte Carlo simuleringer.

Portene ble deretter brukt til å konstruere større systemer. Totalt fem full-addere og fem minority-3 porter ble evaluert og vurdert for cellebiblioteket. Blant de fem minority-3 portene, er en helt ny struktur foreslått som bruker de samme lekkasjebegrensende prinsippene som i ST porter.

Resultater

For større kretser ble én seriell (ripple-carry) og to parallelle (Brent-Kung og Kogge-Stone) addisjonskretser evaluert basert på areal, ytelse, effektforbruk og energieffektivitet. Analyser av disse viste at seriell addisjon kan være mer energieffektivt enn parallell, med samme ytelse, hvis en økning i forsyningsspenning med omtrent 50mV kan aksepteres. Denne konklusjonen relateres til lignende funn som er dokumentert i [2].

For å vurdere standardcellebiblioteket for større, mer komplekse systemer ble en RISC-V prosessorkjerne evaluert for tilsvarende krav som addisjonskretsene over en rekke forsyningspenninger. Et utlegg av denne vises i figur 5.

Resultatene bekrefter at cellebiblioteket oppnår pålitelig operasjon med svært lavt effektforbruk ved forsyningsspenninger under 100mV, og er en viktig motivasjon til videre utvikling av kretsteknikker for robust laveffekt operasjon. Ytterligere detaljer om arbeidet finnes i masteroppgaven [3] tilgjengelig i databasen NTNU Open.