FPGA-samling:

Vellykket FPGA Meetup i Bergen

Det var Inventas sin tur å invitere til faglig FPGA-samling i Bergen i slutten av november, og fremmøtet var upåklagelig.

I samarbeid med Bergen FPGA Gruppe (tidligere FPGA Meetup i Bergen) tok Inventas jobben med å arrangere en FPGA-samling i Bergen i slutten av november. Målet med disse møtene er å videreutvikle fagmiljøet innenfor FPGA. Samlingen fant sted på Høgskolen på Vestlandet.

God deltagelse

Inventas har et nasjonalt utviklingsmiljø for FPGA, og denne fredagen var flere av deres ansatte på besøk i Bergen. Det åpnet gode muligheter for faglig prat, og ikke minst deling av erfaringer og inspirasjon. – Vi må si oss fornøyd med deltagelsen. Det var 21 påmeldte i tillegg til oss 10 fra Inventas, sier Bjørnar Vasenden, som leder selskapets bergensavdeling.

Ønsker forslag til tema

Det eksisterer som nevnt tidligere en FPGA-gruppe i Bergen, og som fort ble en populær møteplass for elektronikk- og FPGA-utviklere i regionen. En av drivkreftene bak disse arrangementene er FPGA-eksperten Arin Morten Kjempenes. – Det blir fort mye administrasjon med innkalling og arrangement, så vi setter stor pris på at Inventas tok jobben denne gang, sier han.

Kjempenes oppfordrer nå miljøet til å komme med forslag til tema for neste møte gruppen skal ha.

HDLRegression

Fokuset for denne samlingen var på verktøy og metoder som gjør livet lettere for FPGA-utvikleren. Blant ga Marius Elvegård en demonstrasjon av HDLRegression, et verktøy for regresjonstesting og automatisering av build for simulering av HDL-kode. Verktøyet har støtte for flere kjente HDL simulatorer, og håndterer kompileringsrekkefølge og effektiv rekompilering. Ifølge Elvegård er det veldig lett å komme i gang med, og eliminerer behovet for TCL-baserte build scripts.

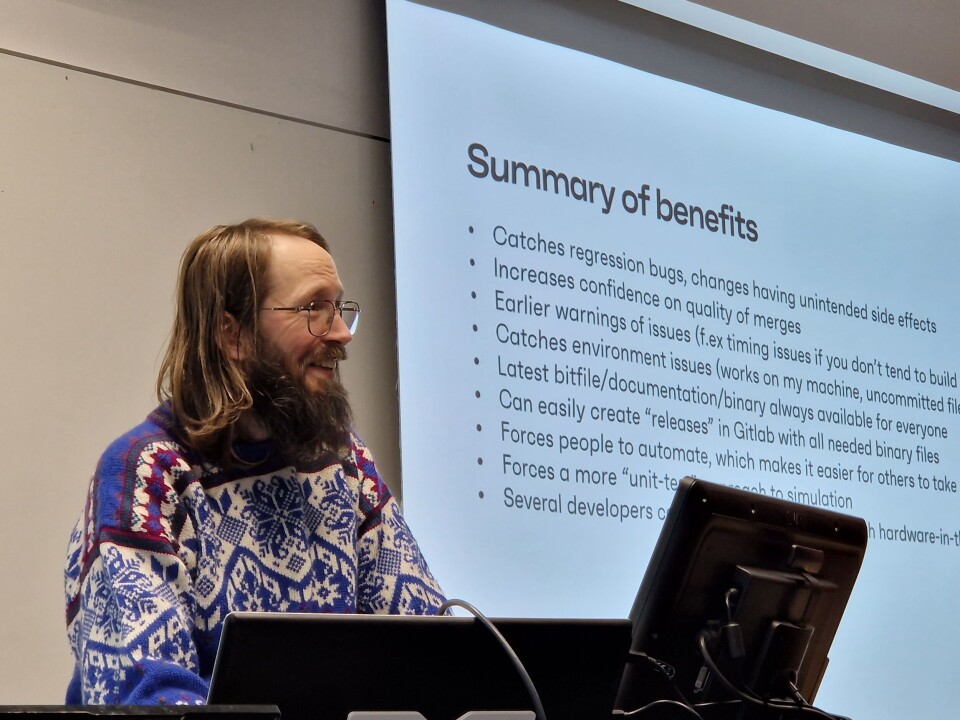

Kontinuerlig integrasjon

For større FPGA prosjekter, spesielt med flere kollaboratører, er det ofte behov for å automatisere kodesjekk, test og simulering, samt syntese og build for FPGA'en. Arild Velure presenterte hvordan dette kan settes opp i en såkalt Continuous Integration (CI) pipeline. Eksemplene var basert på GitLab CI, men er også relevant for andre CI verktøy, ifølge Velure.

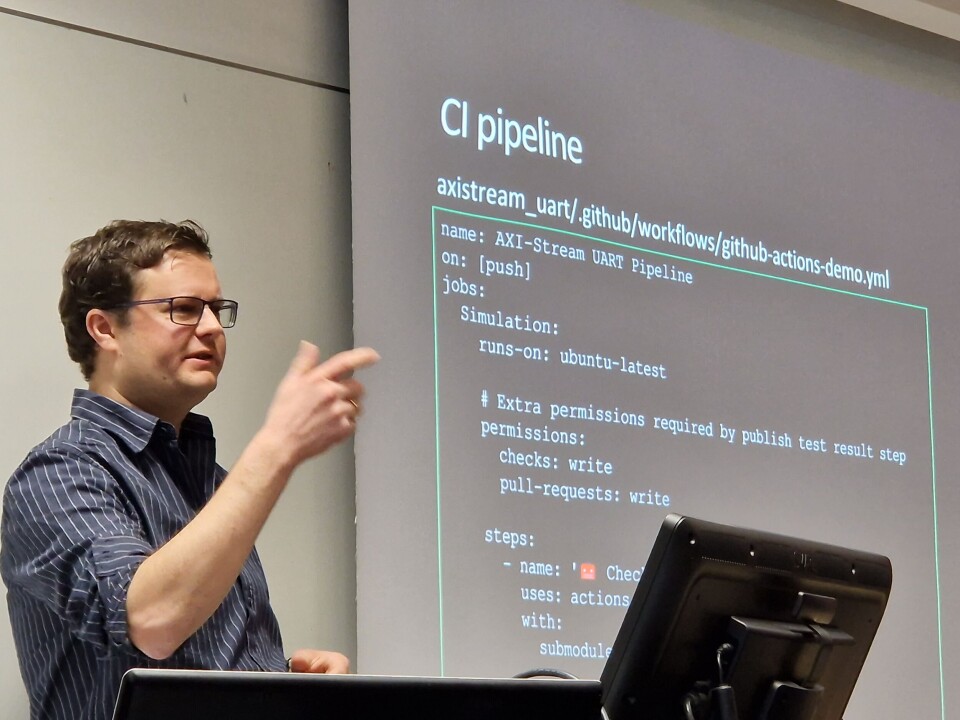

CI-oppsett

Til slutt demonstrerte Simon Nesbø oppsett av build, simulering og CI for en AXI-Stream basert UART modul. AXI-stream er en anvendelig standard for moduler som enten forbruker eller produserer datastrømmer, og har i tillegg veldefinerte «handshake»-mekanismer.

Hva som vil blir presentert på neste møte i Bergen FPGA Gruppe, og når det blir, kommer vi tilbake til.