Halvlederdesign:

Gjennombrudd i design av kryogene CMOS-kretser

Bransjesamarbeid har resultert i vellykkede modifikasjoner av transistormodeller for utvikling av kretser for kryogene temperaturer.

I et pionerarbeid mot å revolusjonere kvantedatabehandling og forbedre energieffektiviteten til datasentre, har Semiwise, sureCore og Cadence samarbeidet for å overvinne kritiske utfordringer i utviklingen av kryogene CMOS-kretser.

Samarbeidet har kulminert i en vellykket modifikasjon av transistormodeller på GlobalFoundries 22FDX i Cadence Spectre-simuleringsplattform, og muliggjør dermed prosessen med simulering og verifisering av analoge, blandede signaler og digitale kretser ved kryogene temperaturer, skriver de tre selskapene i en pressemelding.

Milepælen nådd i dette samarbeidet har sitt utspring i Semiwise Innovate UK-prosjektet "Development of CryoCMOS to Enable the Next Generation of Scalable Quantum Computers", der Semiwise laget de første robuste SPICE-transistormodellene designet for å fungere i ekstreme kryogene miljøer. Dette fremskrittet mener de er sentralt for kvantedatabehandling, og kan øke det potensielle antallet qubits i et system drastisk og utvider beregningsevnene som er nødvendige for å takle komplekse, virkelige problemer betydelig, heter det.

– Vi var i stand til å utvikle produksjonsdyktige design for kryogene CMOS-kretser ved å bruke kryogene transistormålinger utført av Incize sammen med en ledende kommersiell TCAD-simulator. Dette tillot oss å lage kompakte transistormodeller av PDK-kvalitet som inkluderer hjørner og mismatch, uttaler professor Asen Asenov, administrerende direktør i Semiwise.

– Det kritiske lagringselementet, bitcellen, må i hovedsak behandles som en analog krets som er veldig følsom for prosessvariabilitet og mismatch, kommenterer sureCore-sjef Paul Wells. – Når vi utvikler nye minnedesign og deres tilknyttede kompilatorer, må vi kjøre tusenvis av statistiske kretssimuleringer for å garantere produksjonskvaliteten og påliteligheten til IP-en vår, legger han til.

– Vi er begeistret over å kunne jobbe med Semiwise og sureCore i å utvikle modeller i Spectre simuleringsplattform for bruk på kryogene CMOS-kretser, sier Tom Beckley, direktør for Custom IC & PCB Group, Cadence, som er fornøyd med at simuleringsplattformen nå har kalibrerte SPICE-modeller for kryogene miljøer.

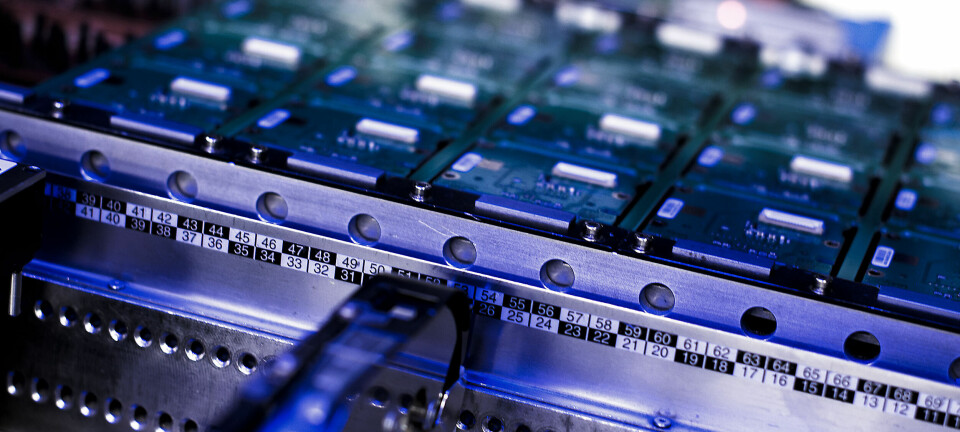

Den første 22FDX SRAM tapeouten fra sureCore for å validere både rekarakteriserte standardceller og en rekke innebygde minne-IP i rammen av Innovate UK CryoCMOS-prosjektet, aktivert av modifikasjonene i Cadence's Spectre Simulation, er planlagt tidlig i 2024. Denne utviklingen er et godt utgangspunkt for samarbeidende innovasjon og fremtidige fremskritt innen kvantedatabehandling og halvlederteknologi, heter det.