Systembrikke for den andre 5G-bølgen

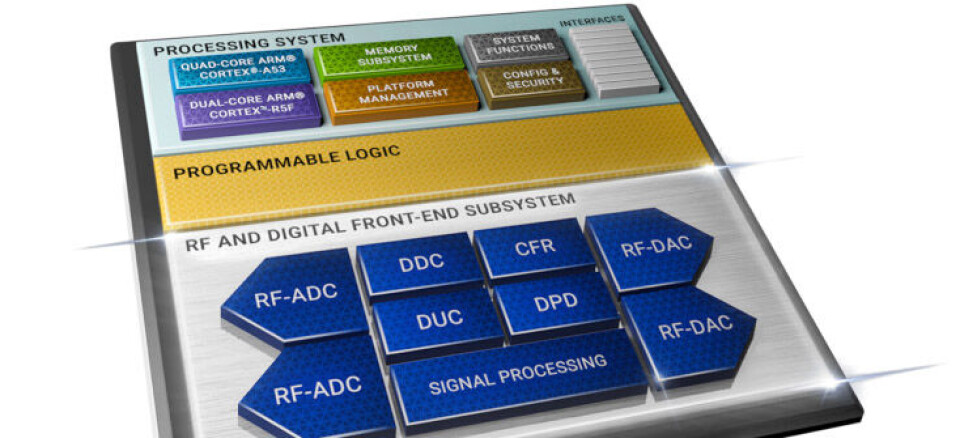

Mindre programmerbar logikk, men mer harde blokker for 5G-radio. Slik kan du beskrive Zynq RFSoC DFE, det siste medlemmet av Xilinx-familien med systemkretser som vil finnes i 5G-produktene som skal rulles ut neste år.

Denne artikkelen er 2 år eller eldre

Zynq-familien var opprinnelig en FPGA-krets der en liten del av silisiumoverflaten var okkupert av to ARM-kjerner pluss at du kunne få rask kommunikasjon med omverdenen. Gjennom årene har de harde blokkene fått mer plass for å øke ytelsen, blant annet har det vært en modell med AD- og DA-omformere for RF-applikasjoner.

– Vi har gått bort fra den forrige strategien for å redusere strømforbruket og øke integrasjonen, sier Gilles Garcia i Xilinx.

Versjonen som kom i 2018 gikk opp til 4 GHz og er i mange av de tidlige 5G-produktene i blant annet Sør-Korea.

For å konkurrere med ASIC’er når volumene øker, har Xilinx utviklet harde blokker for hele mottaker- og senderkjeden, pluss at frekvensområdet er økt til 7,125 GHz (FR1). I Zynq RFSoC DFE, der DFE står for Digital Front End, er det meste av silisiumoverflaten opptatt mens den programmerbare logikken får lov til å spille andrefiolin.

Samtidig er kretsen designet slik at det er mulig å koble fra alle harde blokker og erstatte dem med kode som går i den programmerbare logikken. Det åpner for å styre utviklingen av de nye versjonene av 5G-standarden som utgis årlig, men også produkter som må tilpasses for et bestemt marked eller en applikasjon.

Kretsen støtter en båndbredde på 400 MHz over åtte frekvensbånd i både uplink og downlink (8T8R).

For høyere frekvensbånd, dvs. FR2, kan kretsen gi en mellomfrekvensbåndbredde på 1600 MHz.