Mikroelektronikkprisen 2023:

Hvordan gi IoT-enheter med ultralav forsyningsspenning et fungerende minne?

Tingenes internett eller Internet of Things på engelsk, ofte forkortet IoT, er et system bestående av fysiske enheter som kommuniserer trådløst med hverandre. Men alle noder trenger strøm, og helst så lite som mulig.

I dag finner vi IoT-enheter nesten overalt; i industrien

(f.eks. til overvåkning av maskiner), i helse- og omsorgssektoren (f.eks. for

overvåking av puls, temperatur og lignende hos pasienter, eller pacemakere), i

hjemmet, og til og med på vår egen kropp i form av smartklokker!

Fellesnevneren er at de gjerne har en eller flere sensorer som brukes til å hente informasjon fra omgivelsene. Denne informasjonen brukes deretter av enheten selv, av andre enheter den kommuniserer med, eller av en menneskelig bruker til å ta en beslutning om hvorvidt noe skal gjøres (og i så fall hva).

Avhengig av batterier

IoT-enhetene er små og selvstendige, altså ikke koblet til strømnettet, og er derfor avhengige av batterier for å få energien som trengs for å gjøre jobben de er satt til. Innen 2027 anslås det at vi vil ha 29 milliarder påkoblete IoT-enheter på verdensbasis. Hvis vi antar en batterilevetid på 10 år betyr det at vi må bytte batterier i 2.9 milliarder enheter årlig, noe som tilsvarer 8 millioner enheter daglig. Det sier seg selv at dette er både upraktisk og ulønnsomt, særlig når vi samtidig ønsker og forventer en fortsatt utvidelse av Tingenes internett. Og da har vi ikke engang tatt i betraktning at en del enheter vil være plassert på steder det av ulike grunner (høy temperatur, kjemikalier, langt unna, etc.) er vanskelig å nå fram til for å bytte batterier. Selv med økt batterilevetid og redusert energiforbruk kommer vi ikke utenom problemet med at batteriene på et eller annet tidspunkt må byttes. Alternative løsninger er nødvendige, og det er her energihøstere kommer inn i bildet.

Eget kraftverk

Om enhetene kan utstyres med energihøstere som høster energi fra omgivelsene, f.eks. solenergi, energi fra RF-stråling, kinetisk energi (fra maskinvibrasjoner e.l.), eller varme-energi, vil IoT-enheten bli sitt eget lille kraftverk, og behovet for å bytte batterier forsvinner. En kjempeløsning! Problemet er bare at mange energihøstingsløsninger strever med å levere spenninger høyere enn 100 mV, noe som betyr at spenningen man får ut er for lav til å drive de fleste kretser. I dag løses dette som regel ved å legge til en DC/DC omformer i kretsen som «skrur» spenningen opp til et høyere (og dermed mer brukbart) nivå. Dessverre er DC/DC omformere lite effektive, og ofte går flere titalls prosent av energien tapt i konverteringen. Dette er uheldig siden vi har et stramt energibudsjett i disse IoT-enhetene.

Ultralave spenningsnivåer

I masteroppgaven jeg skrev våren 2023, som avslutning av studieløpet mitt ved sivilingeniørstudiet Elektronisk Systemdesign og Innovasjon ved NTNU, undersøkte jeg derfor muligheten for å konstruere kretser som kan fungere på ultralave spenningsnivåer (under 100 mV) slik at behovet for DC/DC omformere fjernes. Mer presist designet jeg en minnekrets av typen SRAM (Statisk RAM), som både kan skrives til og leses fra, siden det å ha litt minne i en IoT-enhet (f.eks. til å lagre måledata før de sendes videre) er veldig nyttig.

Krevende

Det er allerede forsket på kretser for sub-100 mV forsyningsspenning, men mesteparten av dette arbeidet var på kretser som var mye mindre komplekse enn et minnesystem. Og jo mer komplisert kretsen er, desto vanskeligere er det å få til pålitelig og god oppførsel med en ultralav forsyningsspenning.

Utfordringen med ultralave spenninger

Den viktigste egenskapen til et minnesystem er naturligvis at det husker, og at det husker riktig. Hver gang. Informasjonen må derfor forbli uendret i minnet både fram til og etter at det blir lest, uavhengig av hvor kort eller lang tid det er siden informasjonen ble lagret. Det er derfor ekstremt viktig at systemet kan produsere pålitelige nuller og enere, og at det greier å skille dem fra hverandre. I et minnesystem som dette vil 0 representeres ved jordspenningen, mens 1 representeres ved forsyningsspenningen.

Mindre rom

En høy forsyningsspenning gir stor forskjell i spenningsverdi mellom 0 og 1. Det gjør det lettere å tolke ting riktig. Er forsyningsspenningen på 1 V og vi har et avvik i den logisk høye verdien på 50 mV, altså at signalet har spenningsverdi 950 mV, vil det fortsatt være veldig lett å avgjøre at dette er ment å representere 1 og ikke 0. Er forsyningsspenningen derimot på 100 mV og vi har et avvik i den logisk høye verdien på 50 mV, altså at signalet har spenningsverdi 50 mV, vil det være like nærliggende å tenke at den skulle vært 0 mV som at den skulle vært 100 mV. En lavere forsyningsspenning betyr altså at vi har mindre rom for unøyaktighet og feil i signalverdier, målt i absoluttverdi, før det utgjør et så stort utslag at vi ikke kan avgjøre verdien. Det setter et mye høyere krav til robusthet og nøyaktighet i kretsen, og gjør designet mer krevende.

Terskelspenningen

I tillegg til mindre spenningssving, altså differansen mellom største og minste mulige spenning i systemet, er det også en utfordring at den maksimale spenningen vi har i kretsen er så lav. Det sentrale her er terskelspenningen til transistorene vi bruker. Terskelspenningen er definert som den minste gate-til-source spenningen, det vil si spenningsforskjellen mellom gate-pinnen og source-pinnen på transistoren, som trengs for at transistoren skal være «på». Når transistoren er på har vi en tilnærmet lukket krets, dvs. null motstand, mellom drain-pinnen og source-pinnen på transistoren, slik at strømmen kan gå uhindret gjennom og vi har null spenningsfall.

Terskelspenningen vil variere noe fra en transistorteknologi til en annen (jeg brukte en 22 nm FD-SOI teknologi). Mindre variasjoner forekommer også innad i samme transistorteknologi, påvirket av faktorer som tykkelsen på gate-oksidet og temperatur. For dagens transistorteknologier kan 100 mV uansett antas å være et godt stykke under terskelspenningen. Hvis vi bruker energihøstere som ikke kan levere en forsyningsspenning på mer enn 100 mV vil den største spenningsforskjellen vi kan lage være på 100 mV. Altså vil transistorene, forenklet sett, alltid være av! Heldigvis er virkeligheten mer komplisert enn som så. Transistoren slutter nemlig ikke helt å lede strøm når gate-til-source spenningen går under terskelspenningen, men strømmen minker betraktelig: Når vi er under terskelspenningen, avtar strømmen eksponentielt i takt med at gate-til-source spenningen avtar. Siden det fortsatt går noe strøm kan vi designe kretser som opererer for ultralave forsyningsspenninger. Dessverre gjør det eksponentielle forholdet mellom strøm og gate-til-source spenning at kretsen blir mye mer sensitiv til små variasjoner i gate-til-source spenningen. Det setter høye krav til presisjon i kretsen.

Framgangsmåte, eller «hvordan designe en krets for ULV»

I tillegg til å kunne lagre/huske enten 0 eller 1, må det være mulig å både lese fra en spesifikk adresse i minnet (uten å endre verdien som er lagret der!) og å skrive til en fritt valgt adresse i minnet (så vi kan lagre ny informasjon). Hvis spenningsverdien til et eller flere interne signaler avviker for mye fra ideell verdi (jord (0) eller forsyningsspenning (1)), vil det øke sjansen for at neste ledd i kretsen ikke greier å produsere riktig utsignal. Slik kan en liten feil vokse seg større gjennom kretsen. Dette kan i verste fall føre til at feil adresse blir aksessert, at feil verdi lagres, eller at feil verdi leses ut. Skjer dette fungerer ikke minnet lenger som det skal.

Første trinn i mitt arbeid for å lage en SRAM for så lave spenninger var å finne en robust kretstopologi, slik at kretsen er minst mulig sårbar for variasjoner (som vi forventer at kommer). Valget landet på å bruke en D-latch (D lås) som grunncelle i minnet. Denne ble igjen bygget opp av logiske porter, av typen NOT og NAND. En logisk port defineres av funksjonen den skal utføre (f.eks. skal en NOT port gjøre slik at utgangssignalet er det inverterte av inngangssignalet), og man kan derfor konstruere den samme logiske porten på mange ulike måter. Lotze og Manoli fant at å bruke en Schmitt Trigger (ST) topologi reduserte avviket i utgangsverdi i logiske porter for sub-100 mV spenningsforsyninger. Siden avvikene i signalverdi lett forplanter seg videre i kretsen er dette en viktig egenskap for å skape en robust krets.

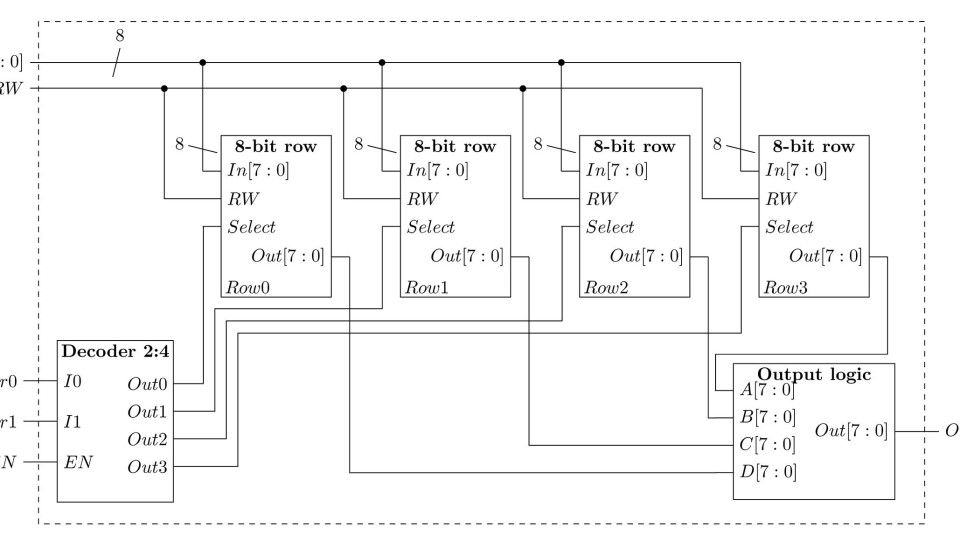

I et minne er det ikke vanlig å skrive til en og en bit av gangen, men heller til et helt «ord» (en rekke med et gitt antall bits). Jeg brukte en ordlengde på åtte bit, og satte derfor åtte D-latcher sammen med litt logikk for kontroll av lesing/skriving for å konstruere lagringsplassen på en adresse i minnet. For å velge riktig ord i minnet basert på adressen brukeren oppgir, konstruerte jeg en standard dekoderkrets. Jeg designet også en egen krets for å sørge for at utgangssignalet til SRAMen ikke hadde flere drivere. Blokkdiagrammet i figur 2 viser hvordan dette blir seende ut for den minste størrelsen SRAM som ble konstruert (4 ord).

En kombinasjon av matematisk analyse (blant annet med utgangspunkt i arbeidet til Lotze og Manoli) og simulering på kretsskjematikken i verktøyet Cadence Virtuoso resulterte i et gitt sett med bredder og lengder for transistorene i de logiske portene. For en mer detaljert analyse kan du lese masteroppgaven min (lenke kommer lenger ned i teksten), men kort forklart er det slik at forholdet mellom transistorstørrelsene innad i kretsen avgjør oppførselen. Videre er «mismatch» omvendt proporsjonalt med transistorarealet, slik at en større transistor blir mindre påvirket av små avvik i produksjonen som forekommer når kretsen blir «tapet ut» (tapet ut = laget) som en fysisk chip. Vi skal komme tilbake til fenomenet «mismatch» når vi ser på resultatene.

Etter å ha funnet transistordimensjoner som virket lovende i skjematikksimuleringene, laget jeg utlegg (layout) av kretsen. Dette er en prosess der man tegner opp hvordan kretsen skal bli konstruert rent fysisk (et lag metall her, et lag med polysilisium der osv.), slik at man kan kjøre simuleringer på dette designet. Når simuleringsverktøyet har informasjon om avstanden mellom de ulike komponentene og hvordan de ligger i forhold til hverandre, kan den ta med effekter som parasittisk kapasitans. Dette fører til mer realistiske resultater, og er det nærmeste vi kommer å gjøre målinger på en fysisk krets uten å faktisk «tape ut» kretsen (dvs. produsere en chip med kretsen på).

Resultater

Under produksjonen av en transistorkrets, som vanligvis skjer på en waferfabrikk i utlandet over en periode på flere måneder, vil det kunne oppstå feil og avvik som gjør at kretsen ikke ender med å bli eksakt lik designet. Dette er uunngåelig, og kretsene designes derfor for å kunne fungere selv med noe avvik (gitt av fabrikkens informasjon rundt graden av nøyaktighet og presisjon de kan garantere). Vi skiller mellom prosessvariasjoner, altså systematiske feil i produksjonen som påvirker alle transistorer av samme type på samme måte (f.eks. ved å gjøre alle NMOS-transistorer litt sterkere enn designet tilsier), og transistor mismatch som er små avvik i den enkelte transistor som kan påvirke alle transistorene ulikt. Ved å kjøre tester av kretsen der vi simulerer disse effektene kan vi verifisere at kretsen antagelig vil fungere dersom vi sender den til fabrikken for produksjon.

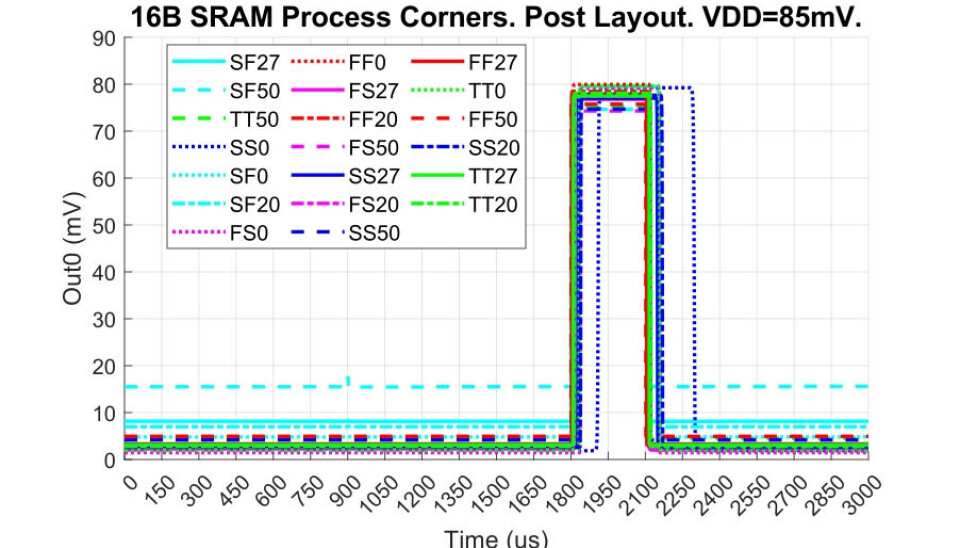

Resultatene fra simuleringene av mismatch og prosessvariasjoner viste at en 16 ord (16B) versjon av minnekretsen (etter fysisk utlegg) fungerte godt med en forsyningsspenning på bare 85 mV. Det er veldig lovende! Bedre balanse i driverstyrken mellom pull-up (PMOS) og pull-down (NMOS) nettverket i de logiske portene ville antagelig resultert i en enda lavere minimumsspenning.

Hvor rask kretsen er varierer en del, som vi ser av resultatet fra simulering av prosessvariasjon vist i figur 3, men så lenge man alltid venter lenge nok til at den i det tregeste scenarioet er klar er ikke dette et stort problem.

Vil du lese mer om hvordan jeg gikk fram for å designe kretsen, og hva simuleringene ga av resultater? Da kan du ta en titt på masteroppgaven min, som du finner her: https://ntnuopen.ntnu.no/ntnu-xmlui/handle/11250/3089837

Hva bringer framtiden for kretser med ultralave forsyningsspenninger?

Jeg tror vi kommer til å se et fortsatt, og forhåpentligvis økt, fokus på design av diverse kretser for ultralave forsyningsspenninger framover. Dette vil bidra til å muliggjøre enda flere innovative energihøstingsløsninger for IoT, ettersom kravet til levert forsyningsspenning kan senkes.

Hvor lavt vi kommer til å kunne presse forsyningsspenningen for ulike kretser er vanskelig å spå. Andre som har sett på mindre kompliserte kretser (bestående av færre logiske porter, både totalt og i kritisk sti) har i simulering fått til gode resultater med forsyningsspenninger på bare litt over 60 mV. Dette mener jeg viser at det burde være mulig å få laget kretser med samme grad av kompleksitet som SRAMen jeg designet for lavere forsyningsspenninger enn det som ble oppnådd i min masteroppgave, og jeg gleder meg til å se hva andre får til på dette området de neste årene. Ekstra spennende blir det å se flere resultater fra målinger, og ikke bare simulering, siden dette vil gi enda sikrere bevis på at ultralav forsyningsspenning er oppnåelig og brukbart.