Fagartikkel

MCU som komplett AI-SoC

Integrasjonsutfordringen: Hva som egentlig skal til for at en generell MCU skal fungere som en komplett AI SoC.

Bruken av AI i endepunktsenheter kan endre verdien deres

betydelig. På den medisinske arenaen kan bærbare AI-enheter ta påvisning og

diagnostisering av alvorlige tilstander som atrieflimmer ut av klinikken og inn

i pasientens hverdag for overvåking. Og ved å bruke AI-algoritmer kan

høreapparater transformeres fra en enkel forsterker til en intelligent

vokaldiskriminator, som isolerer stemmen til personen av interesse, mens de

kansellerer all annen støy og stemmer, eller demper dem i den soniske bakgrunnen.

AI i endepunktet

Disse AI-egenskapene kan multiplisere verdien av nesten alle typer bærbare og kroppsnære batteridrevne produkter. Og ved endepunktet kan AI-funksjoner ofte ikke utføres i skyen på grunn av effekt, ventetid, personvern, trådløs rekkevidde, sikkerhet og kostnader. Slike enheter trenger lokal AI-prosesseringsevne.

Men en vellykket lokal implementering av AI i disse produktene må finne en vei forbi de alvorlige designbegrensningene med plass og effekt. Bærbare enheter som øreplugger, ringer, smarte briller og pasientmonitorer har små kabinetter som kan romme få komponenter og bare et lite batteri.

I «før-AI» tid var mange av disse typer produkter (selv om de var utstyrt med færre funksjoner og fysisk større) basert på generelle mikrokontrollere eller mikroprosessorer som kunne integrere hovedfunksjonene. Integrasjon hjelper designeren med å nå sine mål for plass og effekt, samtidig som den reduserer antall komponenter og kretskortavtrykk.

Integrering – en utfordring

I AI-æraen er integrering av systemfunksjoner i en MCU for generell bruk fortsatt en svært ønskelig måte å spare plass og strøm på. Men en AI MCU må integrere enda flere funksjoner enn tidligere konvensjonelle MCUer, samtidig som den ivaretar det ultralave strømforbruket som gjør at enheter med små batterier kan kjøre AI i endepunktet uten å ofre oppetid mellom ladinger.

Dette er ikke så enkelt som å skru AI-evne på en eldre MCU-arkitektur. Alif Semiconductor, som ble grunnlagt i 2019 for å lage en ny generasjon AI-aktiverte MCUer for endepunktenheter, har hatt fordelen av å tenke fra bunnen av om hvordan man integrerer AI i en MCU. Denne tenkningen gjenspeiler de hundrevis av samtalene der OEMer har beskrevet for Alif faktorene som påvirker deres valg av MCU for å tjene som en AI-systembrikke (SoC) for batteridrevne endepunktenheter. Her er fire av de viktigste av disse faktorene.

1. Nevral prosesseringsakselerasjon må være tett koplet til CPUen

MCU-markedets første respons på kundenes etterspørsel etter AI-funksjonalitet var å utvikle AI-programvareutviklingssett (SDK) for å gjøre det mulig for AI/maskinlærings- (ML) algoritmer å kjøre på den samme Arm® Cortex®-M CPU som også utførte konvensjonelle kontrollfunksjoner. En MCU for endepunkt-ML-applikasjoner trenger imidlertid en nevral prosessorenhet (NPU): denne typen prosessorer er optimert for multiplikasjonsakkumuleringsoperasjoner (MAC) som er brødet og smøret for nevrale nettverksapplikasjoner. En innvevd CPU alene vil slite med meningsfulle ML-arbeidsbelastninger fordi konklusjoner avledet fra det svært parallelle ML-nettverket må løses på en seriell måte, noe som tar overdreven tid mens det brenner mye energi.

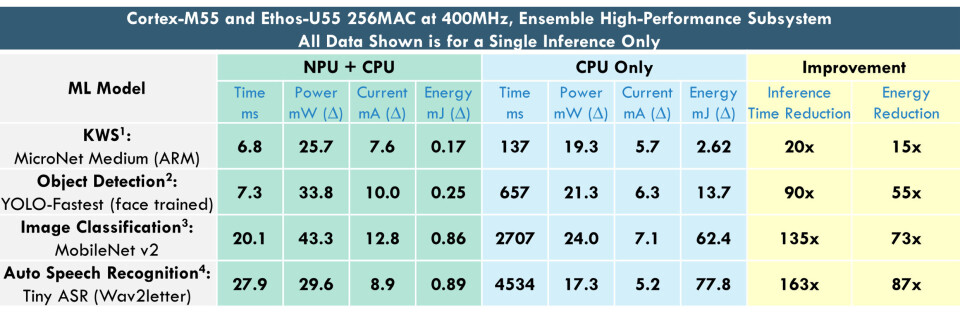

Fotnoter til Figur 1:

1) KWS: Fra ARM MicroNets notat. Kvantisert int8, trenet på ‘Google Speech Commands’ datasett. Modellavtrykk: 154KB MRAM, 28KB SRAM

2) Objektdeteksjon: 192x192 gråskalaoppløsning & farge. Kvantisert int8, trenet på ‘WIDER FACE’ datasett. Modellavtrykk: 431KB MRAM, 433KB SRAM

3) Bildeklassifisering: 224x224 24bit oppløsning % farge. Kvantisert int8, trenet på ‘ImageNet’ datasett. Modellavtrykk: 3.552KB MRAM, 1.47KB SRAM

4) ASR: Tiny Wav2letter beskåret inn i ARM's ML demo app, kjørt på ASR brukstilfelle. MRAM=2346,06KB (stort sett Vela optimalisert fra 3903,43KB), SRAM=1197,20KB

Figur 1 illustrerer kontrasten i AI-ytelse mellom en MCUs CPU og NPU. Alif Semiconductors MCU-familie Ensemble bruker den moderne Cortex-M55 CPU-kjernen sammen med en Ethos™-U55 NPU-tilleggsprosessor. Tallene viser en enkelt ML-slutning (inferens) for fire trente ML-modeller som kjører på en Ensemble MCU: Modellene representerer operasjonene som kreves for søkeordoppsporing, objektdeteksjon, bildeklassifisering og talegjenkjenning.

Cortex-M55 som brukes i Alif MCUer er blant de beste innvevde CPU-arkitekturer, og gir gode tall som allerede er i størrelsesorden 5 ganger bedre for ML-arbeidsbelastninger enn tidligere generasjoner Cortex-M-CPUer. Uansett så bra som Cortex-M55 er, avsløres imidlertid en betydelig ekstra ytelsesøkning av tallene i de gule kolonnene: Nærmere og enda mer enn to størrelsesordener forbedring ved bruk av NPU+CPU sammenlignet med kun CPU. Ved å merke seg at Cortex-M55 allerede yter rundt 5 ganger bedre enn tidligere, mye brukte Cortex-M-arkitekturer, er det rimelig å multiplisere disse gevinstene igjen med 5x. For talegjenkjenning vil det være rundt 800 ganger raskere og 400 ganger mindre energi per slutning sammenlignet med eldre Cortex-M CPUer.

En annen viktig faktor ved en tett kobling av NPU til CPU er programvareutviklingsmiljøet. Det er mange alternativer for å distribuere proprietære og tredjeparts NPU-kjerner i SoCer. OEMer er imidlertid veldig tydelige: De ønsker ikke å omstrukturere hele utviklingsinfrastrukturen for å jobbe med en ny arkitektur kun for AI/ML-arbeidsbelastninger, noe som krever bruk av nye verktøykjeder og nye instruksjonssett.

Hvis de allerede jobber i Arm- økosystemet for innvevde styrefunksjoner, ønsker de å forbli i Arm-økosystemet for AI/ML-funksjoner også. Å kombinere en Cortex-M CPU med en Ethos-U NPU, begge fra Arm, oppnår dette kravet.

Faktisk er Ethos-U NPU i hovedsak en tilleggsprosessor som integreres sømløst med Cortex-M CPU. Arm Vela-kompilatoren vil automatisk dele ML-arbeidsmengden mellom seg, med 95 % eller mer som vanligvis faller på NPU. En stor sidegevinst er at Cortex-M CPU kan sove eller utføre annet arbeid mens ML-slutningen blir løst.

2. Integrasjonen må omfatte hele systemet

Det er rimelig å si at NPU sannsynligvis vil være sentrum for oppmerksomheten i en integrert AI/ML MCU. Men hva som er integrert rundt prosesseringskjernene, og spesifikt hvordan integrasjonen er laget, er veldig viktig. Øverst på listen er minne og periferiutstyr.

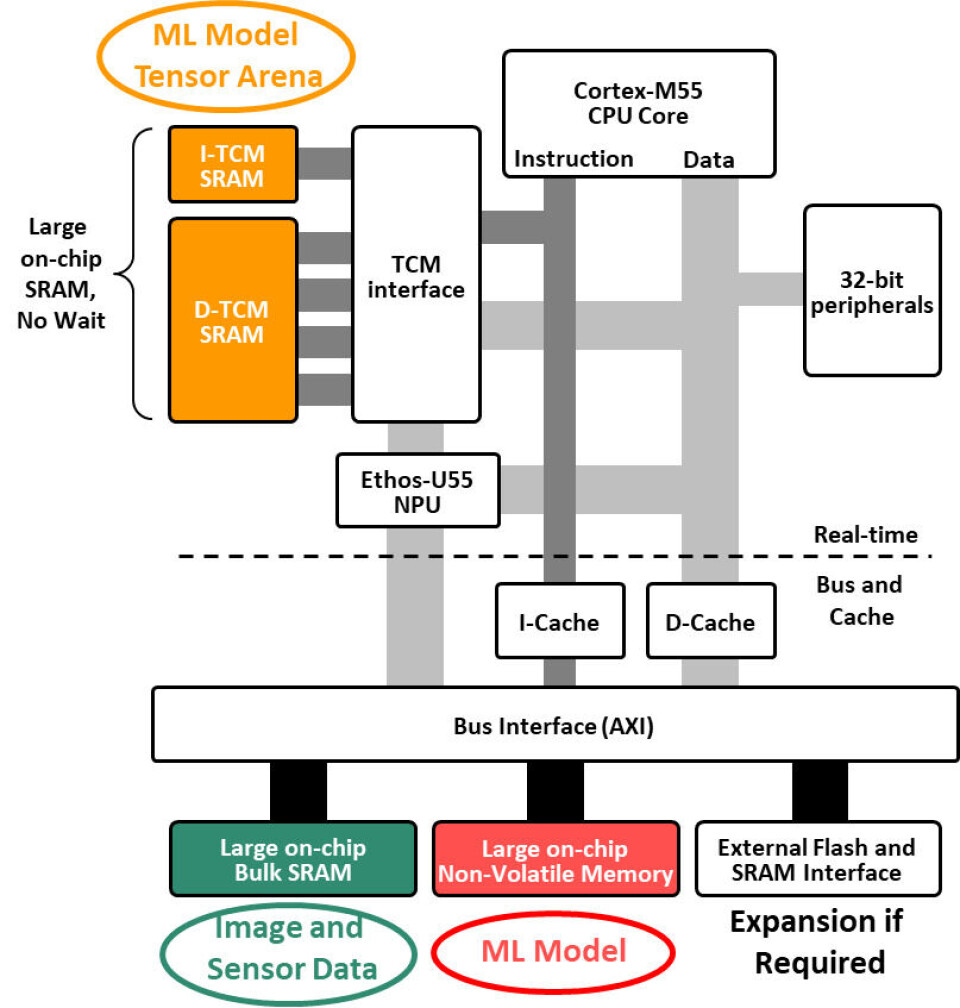

Figur 1 viste at forbedret prosesseringsevne er nøkkelen til høy ytelse og strømeffektivitet, men uten et optimert minnesystem bak vil resultatene ikke oppfylle forventningene.

En forenklet visning av Ensemble MCU-minnetopologien er vist i figur 2. Den øvre halvdelen representerer sanntidsdelen med svært raskt Tightly Coupled Memory (TCM) koblet til CPU- og NPU-kjernene. For raske slutningstider må disse TCM SRAM-minnene være tilstrekkelig store til å holde ML-modellens tensorarena.

Den nedre halvdelen av diagrammet viser andre systemminner koblet sammen med en felles høyhastighetsbuss. En stor, delt bulk SRAM er nødvendig for å holde sensordata, for eksempel inngang fra et kamera og mikrofoner, og et stort ikke-flyktig minne inneholder selve ML-modellen pluss applikasjonskode. Når store on-chip-minner distribueres på denne måten for å minimere konkurrerende busstrafikk, blomstrer samtidige minnetransaksjoner, flaskehalser fjernes, minnetilgangstider minimeres og strømforbruket er kompatibelt med bruk av et lite batteri.

Riktig periferisett er også kritisk for MCUer i ML-applikasjoner i endepunkt som ofte opererer i ett eller flere av de "tre V"-domenene: syn, stemme og vibrasjon. Dette betyr at det kreves tilkobling til bildesensorer, mikrofoner, treghetsmåleenheter og mer, i tillegg til tradisjonelle MCU-periferiutstyr som høyhastighets serielle kanaler, analoge grensesnitt og skjermforbindelser.

For AI-baserte endepunktenheter bør alle disse funksjonene integreres i MCU.

Integrering av hele systemet eliminerer ikke bare behovet for ekstra strømskinner og strømkonvertering som en ekstern Power Management IC (PMIC), men gjør det også mulig å kontrollere effekten dynamisk på et mye mer granulært nivå på brikken – og dette er den tredje ønskelig funksjon på en integrert AI MCU.

3. Adaptiv kraftstyring for å forlenge batteritiden

Alif erkjente tidlig at konsentrasjonen av lokal ML-kapasitet ved endepunktet vil skyte i været i nær fremtid, samtidig som den fysiske størrelsen på disse produktene raskt vil krympe, spesielt for kroppsnære enheter, noe som innebærer bruk av mindre og mindre batterier.

Alifs tilnærming til å forlenge batterilevetiden for å løse dette problemet tok flere former. To gode eksempler er:

- Partisjonering av systemet slik at en laveffektdel av brikken alltid kan være på, men fortsatt tilby robust databehandlingskapasitet, slik at den selektivt kan vekke en del av brikken med mye høyere ytelse for å utføre tunge arbeidsbelastninger – og deretter gå tilbake til dvale

- Kraftstyringssystemet slår dynamisk på bare de deler av brikken som er nødvendig, og slår dem av når det ikke er nødvendig, alt på et høyoppløselig nivå.

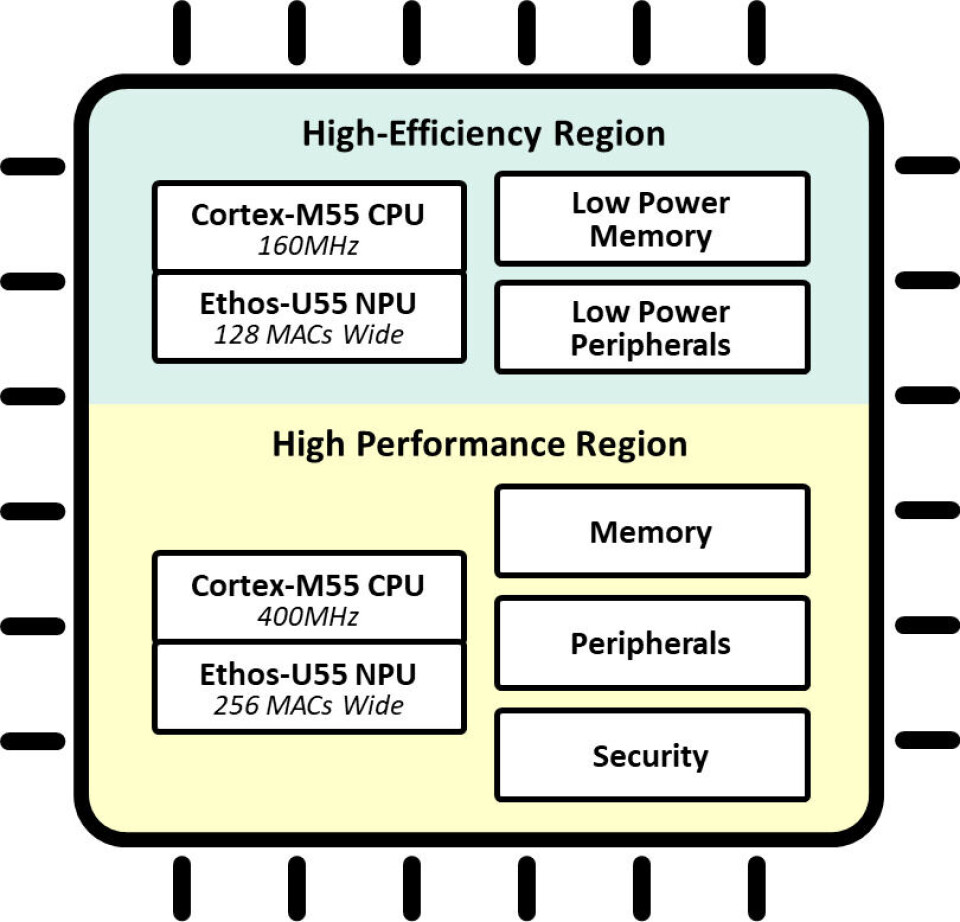

For å lette denne funksjonsdelingen har mange Ensemble MCUer to par Cortex-M55+Ethos-U55-kjerner som vist i figur 3:

- Ett i den høyeffektive regionen av brikken, bygget på lavlekkasjetransistorer som alltid kan være på og drives med opptil 160 MHz

- Den andre paret i høy-ytelsesregionen og med drift opptil 400MHz.

For å forestille deg fordelen dette gir, kan du se for deg et smart kamera som kontinuerlig skanner et rom med lav bildefrekvens ved å bruke det høyeffektive kjerneparet for å klassifisere en gyldig hendelse (for eksempel et menneske som faller i gulvet, eller en spesifikk gest) og som vekker høy-ytelsesparet for å identifisere en eller flere personer, se etter blokkerte utganger, ringe etter hjelp og så videre.

I dette tilfellet kan kameraet være på vakt på en intelligent måte, produsere færre falske positiver og forlenge batterilevetiden. Lignende anvendelser for disse to parene med CPU+NPU-kjerner kan komme like godt til nytte innen klassifisering av lyder, stemmer, ord, tekst, vibrasjoner og sensordata i en rekke applikasjoner.

I tillegg bruker alle Ensemble MCUer Alifs aiPM™-teknologi (autonom intelligent Power Management) for å manipulere i sanntid opptil 12 individuelle kraftdomener i brikken etter behov for å matche brukertilfellet som utføres. Bare domener som aktivt utfører oppgaver er slått på (for eksempel de som leverer spesifikke prosesseringskjerner, minner eller periferiutstyr) mens de andre domenene forblir av. Dette blir transparent for programvareutvikleren.

4. Beskyttelse av verdifulle maskinlæringsmodeller og annen IP

Den siste nøkkelfunksjonen som må integreres i en AI MCU for endepunkter er sikkerhetsbeskyttelse. Dette er selvfølgelig for å motstå de alltid tilstedeværende formene for cyberangrep. Men for mange OEMer er den viktigste beskyttelsen for deres IP innvevd i AI-modeller.

OEMer investerer enorme mengder tid og penger i å samle datasett for trening, bygge AI-modeller og utvikle og avgrense slutningsalgoritmer. Dette gir skruppelløse produsenter et sterkt insentiv til å stjele denne kostbare IPen ved å kopiere den fra utilstrekkelig beskyttede produksjonsenheter.

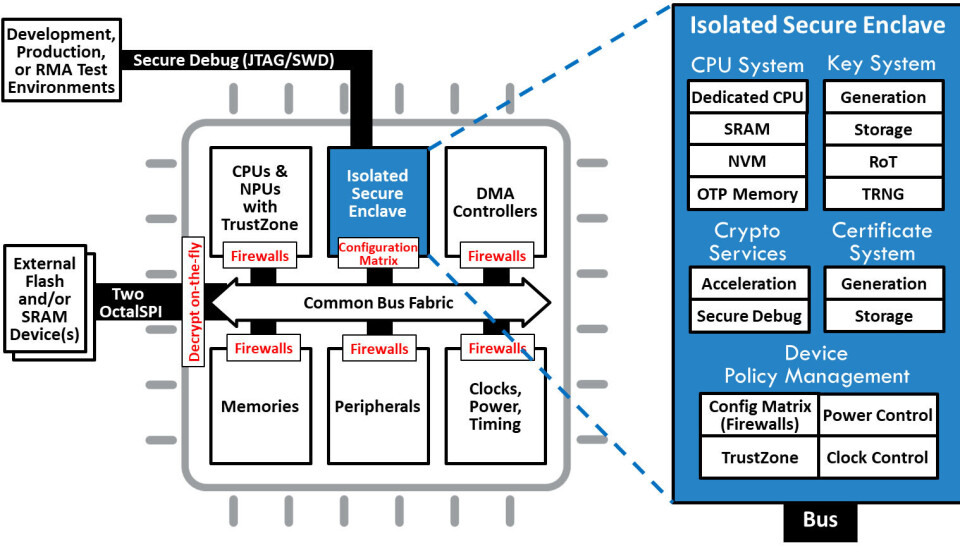

En ekstern, sikker MCU vil gjøre det mulig for OEM å etablere en root-of-trust, administrere hemmelige nøkler og sertifikater, lette en sikker oppstart og så videre. Bruken av en ekstern sikker MCU er en vanlig tilnærming til å bygge inn sterk sikkerhet til konvensjonelle MCU-baserte design, men det er sjelden å finne en fullstendig sikker "enklave" med disse funksjonene, og ikke minst, innvevd i en konvensjonell MCU.

Ikke desto mindre drar batteridrevne og kroppsnære AI-produkter spesielt fordel av plass- og strømbesparelsene og den økte sikkerheten når denne funksjonaliteten er integrert i MCUen. Den sikre enklaven (se figur 4), standard i alle Alif-enheter, er et dedikert isolert delsystem for administrasjon av vitale sikkerhetsfunksjoner, som sikker nøkkeladministrasjon og lagring, sikker oppstart med en uforanderlig Root-of-Trust, attestasjon ved kjøring ved bruk av sertifikater, kryptografiske tjenester for maskinvare, sikker feilsøking, utlesningsbeskyttelse, sikre fastvareoppdateringer og fullstendig livssyklusadministrasjon.

En AI-klar MCU-plattform

Disse fire egenskapene til en AI MCU – tett kobling av NPU og CPU med et standard utviklingsøkosystem, integrering av komplett system, adaptiv kraftstyring og innvevd IP-beskyttelse – er meget etterspurt hos produsentene av batteridrevne endepunktenheter som Alif Semiconductor er engasjert med.

Designere som vurderer Ensemble-familien vil finne et bredt utvalg av skalerbare og kompatible enheter, fra én enkelt CPU-kjerne til firekjerners enheter som støtter Linux®-operativsystemet for å passe til varierte prosjekter samtidig som de muliggjør gjenbruk av programvare på tvers av dem alle.

Se mer på alifsemi.com.