Skalerbar flyttallsprosessor

En ny laveffekt Tensilica DSP-IP tilbyr skalerbar ytelse i en rekke prosesseringsintensive applikasjoner, fra maskinlæring til motorstyring, objektfølging og hyperskala prosessering.

Denne artikkelen er 2 år eller eldre

Rett før helgen lanserte Cadence Design Systems, Inc. den nye Tensilica FloatingPoint DSP familien, som skal ivareta en skalerbar og konfigurerbar løsning, utviklet spesielt for flyttallsorienterte arbeidsoppgaver.

IP-kjernene spenner fra små, ultra-laveffekt til høy-ytelses applikasjoner og skal være egnet i en rekke applikasjoner. Dette kan være energieffektive løsninger for batteridrevne enheter, til applikasjoner innen kunstig intelligens/maskinlæring(AI/ML), motorstyring, sensorfusjon, objektfølging og augmentert virkelighet/virtuell virkelighet (AR/VR) i ulike markeder.

Den nye familien består av fire kjerner: Tensilica FloatingPoint KP1 DSP, Tensilica FloatingPoint KP6 DSP, Tensilica FloatingPoint KQ7 DSP og Tensilica FloatingPoint KQ8 DSP.

Ifølge Cadence har tilbakemeldingene fra pilotkundene vært svært positive.

– Flyttall er vanlig i tekniske beregninger, og danner for eksempel basis for en rekke radarapplikasjoner som prosesserer store eller uforutsigbare datasett, forteller Ian Podkamien, direktør for bilmarkedet hos Vayyar Imaging. – Vi har samarbeidet med Cadence om flere generasjoner av IP-kjerner, og er glad for at de adresserer dette kritiske markedsbehovet og utvider produktlinjen fra Tensilica, fremholder han.

Flyttalls-DSPer som er optimalisert for ulike applikasjoner kan gjøre Vayyars systembrikke-sensorer i stand til å forbedre energieffektiviteten og ytelsen på tvers av så ulike markeder som kjøretøy, eldreomsorg, smarthus, detaljhandel, HLS, robotikk og medisinsk industri, blant andre, sier Podkamien.

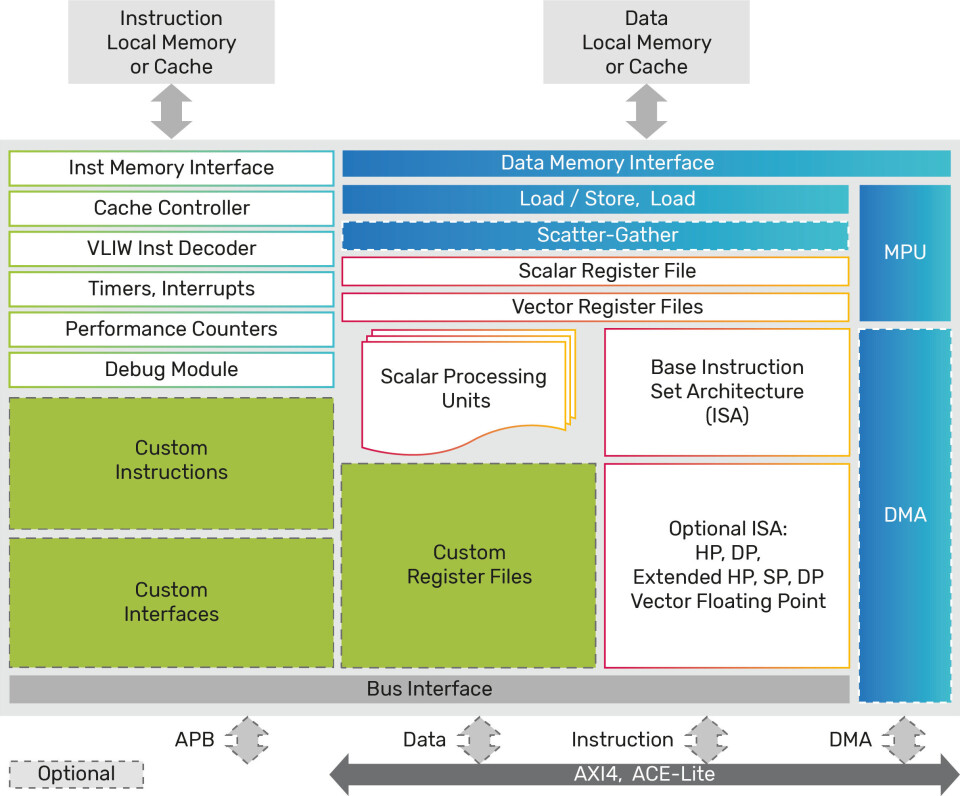

Tensilica FloatingPoint DSP deler en felles instruksjonssettarkitektur (ISA) med en opsjon som finnes i eksisterende Tensilica DSPer, en vektor flyttallsenhet (VFPU). Dette skal fremme programvareportabilitet og gjenbruk, samtidig som man åpner for enkel avlasting av flyttallsoppaver.

De nye flyttalls-DSPene er skalerbare fra 128-bit SIMD til 1024-bit SIMD på plattformene Tensilica Xtensa LX og NX, og skal gi en forbedring på 25% i «fused multiply-add» (FMA) operasjoner sammenlignet med Tensilica fasttalls-DSPer med VFPU add-on.

Ytelsen skal kunne forbedres ytterligere med bruk av Tensilica Instruction Extension (TIE) språk. I tillegg kan flyttalls-DSPene tilby opp til 40% arealbesparelse, sammenlignet med lignende typer fasttalls-DSPer med VFPU, heter det.

Kraftige programvareverktøy som følger med de nye DSPene skal tilby effektiv auto-vektorisering, noe som bidrar til å optimalisere den skalare koden for å kunne anvende de vektorbaserte flyttallsenhetene med liten eller ingen manuell innsats.

Støtte for optimalisert Eigen, NatureDSP, samtidig lokalisering og kartlegging (SLAM) og matematikkbiblioteker skal videre åpne for enklere utvikling av høy-ytelses programvare.