Hacket seg inn i FPGA

En forskergruppe lykkes med å kompromittere krypteringen i Xilinx FPGA. – Et alvorlig sikkerhetsbrudd, sier kilder i miljøet.

Denne artikkelen er 2 år eller eldre

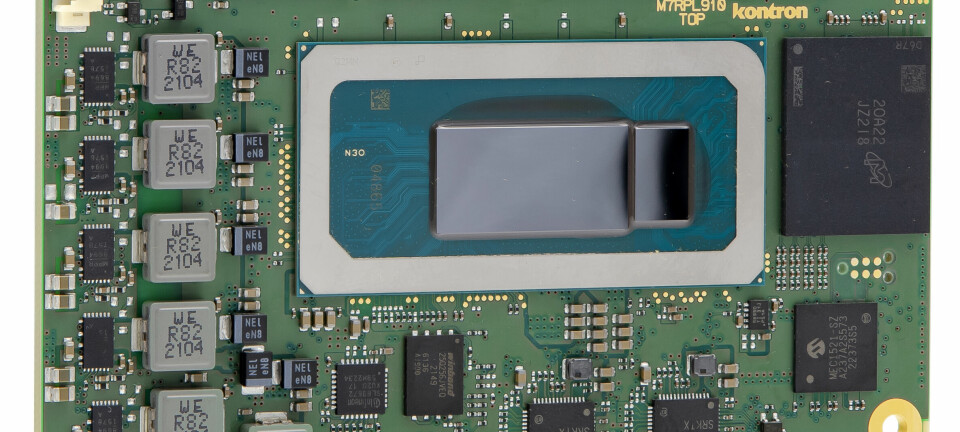

Det ble nylig kjent at en gruppe forskere fra flere europeiske universiteter har publisert en studie der de har lykkes med å bryte ned krypteringen av bitstrømmen i Xilinx 7-serien med feltprogrammerbare portmatriser (FPGA).

FPGA-design er kodet i såkalte bitstrømmer, som konfigurerer logikken i FPGAen. I SRAM-baserte FPGAer lagres bitstrømmen i et eksternt minne og lastes inn i FPGAen ved oppstart. I denne operasjonen må bitstrømmen beskyttes med autentisering og gjerne kryptering. Dersom en angriper lykkes i å kompromittere autentisiteten i bitstrømmen, kan han i verste fall endre funksjonaliteten, implantere maskinvaretrojanere, eller fysisk ødelegge systemet FPGAen er bygget inn i ved å bruke konfigurasjon utenfor spesifikasjonene.

Forskergruppen anvendte nye, «billige» angrepsmetoder mot Xilinx 7-serie og (og Virtex 6-serie) bitstrømkryptering, noe som resulterte i «fullstendig tap av autentisitet og konfidensialitet». Ifølge gruppen krevde ikke angrepet noen avanserte verktøy, og metoden åpnet også for muligheten for et fjernstyrt angrep.

I angrepet manipulerte de den krypterte bitstrømmen til å omdirigere sitt (krypterte) innhold fra logikkmatrisen til et konfigurasjonsregister, som holder de ukrypterte bitstrømdata: Utlesing av konfigurasjonsregisteret ble ikke hindret selv i nærvær av en kryptert bitstrøm uansett, skriver forskerne.

Xilinx skriver i en kommentar til saken at kompleksiteten i angrepet ligner velkjente og gjennomprøvde DPA-angrep mot disse komponentene, og derfor ikke svekker deres sikkerhetsposisjon.

De skriver videre at forfatterne av artikkelen utnyttet mangel på feilutvidelser i AES-CBC-modus og det faktum at konfigurasjonskommandoer, spesielt WBSTAR, kan eksekveres i forkant av autentiseringspassing, og dermed lykkes de å knekke sikkerheten i brikken.

Det skal ikke være mulig å utbedre sikkerhetshullet uten å endre silisiumet. Xilinx har imidlertid gitt ut designanvisninger for å hanskes med problemet.

Zynq-7000 SoC komponenter, og nyere arkitekturer som UltraScale og UltraScale+, Zynq UltraScale+ MPSoC enheter og Versal ACAP skal ikke være berørt av sikkerhetsbruddet, opplyser Xilinx.

Saken blir nå ivrig debattert av utviklere i ulike debattforum verden over.