ESA satser på norsk verifikasjonssystem

ESA på jakt etter bedre verifikasjonsplattformer for FPGA: Velger å fullfinansiere neste utviklingstrinn i norske Bitvis’ verifikasjonsverktøy UVVM. Limet i avtalen var Norsk Romsenter.

Denne artikkelen er 2 år eller eldre

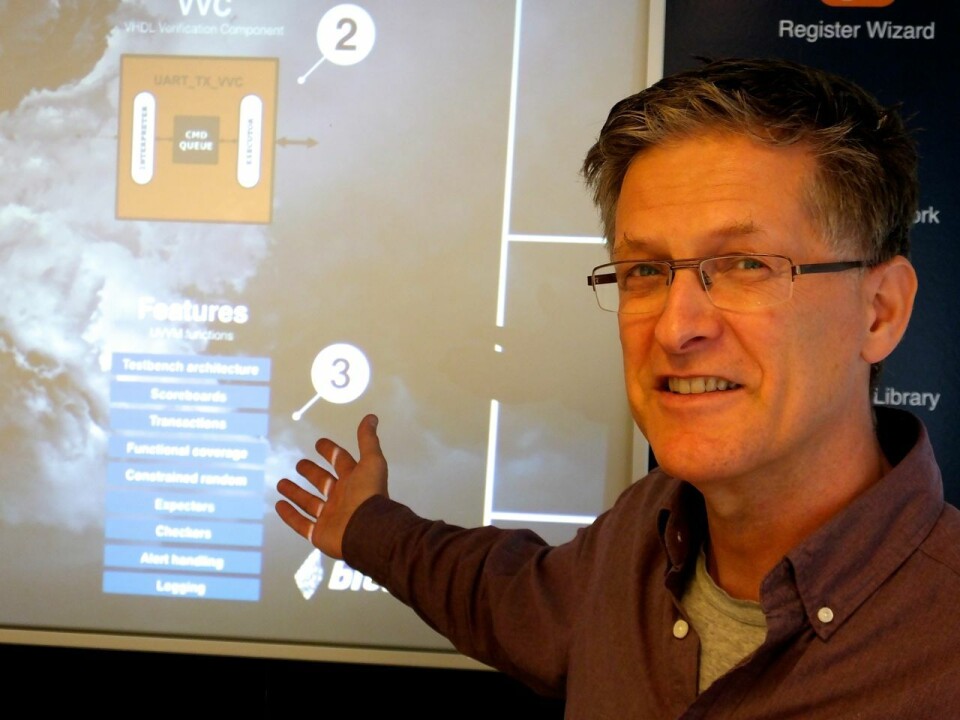

– Dette vil endre verifikasjonsmarkedet, sier daglig leder Espen Tallaksen i Bitvis.

Kontrakten er signert, og prosjektet starter denne uken. – Det er jo i utgangspunktet ekstremt positivt, både fordi vi faktisk får fullt betalt for denne videreutviklingen av UVVM og fordi det viser at ESA tror på systemet, hvilket selvfølgelig er kjempebra markedsføring, sier Tallaksen.

Det som kanskje er enda viktigere er at ESA har planer om å anbefale alle sine leverandører å bruke UVVM, som er et ”open source” verifikasjonssystem, til å verifisere VHDL-kode i FPGAer til ESA-systemer, såfremt de ikke allerede har et velfungerende system, noe det er veldig mange som ikke har. I denne sammenheng kommer Bitvis til å fungere som et samlingspunkt for brukere Europa rundt som tar i bruk produktet. Ikke verst for et lite designsenter fra Norge.

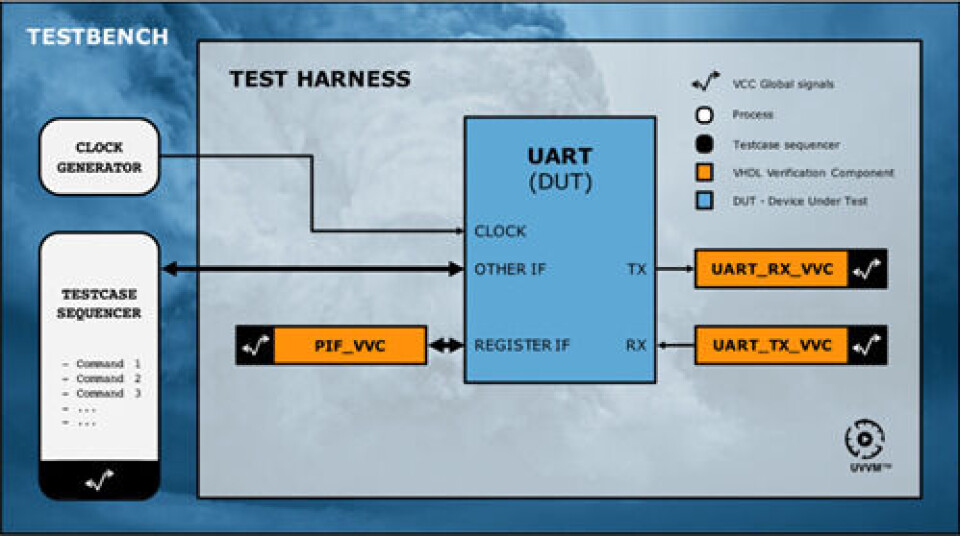

UVVM består av et åpent bibliotek, og et rammeverk med VHDL verifikasjonskomponenter.

Det å lage en testbenk som lager påtrykk og sjekker output på flere grensesnitt på en FPGA samtidig, kan være en kompleks oppgave. For å løse dette har Bitvis utviklet standardiserte verifikasjonskomponenter (VVC) som skal kunne brukes til de fleste oppgaver. Testdriveren (scheduler) gir bare beskjed til VVC om hva som skal trykkes på for eksempel en UART-port, og hva den skal forvente tilbake av data. Dersom responsen er feil, gis en feilmelding.

Alle VVCer har samme arkitektur og standardisert kommunikasjon, og selv om enkelte I/O-typer er mer komplekse, som Avalon med ”split transaction”, vil man kunne bruke samme arkitektur med en liten utvidelse. For øvrig er struktur og eksekvering lik. Dette er basisen i Bitvis’ verifikasjonsløsning.

– Vi sendte en forespørsel til ESA for å utvide og legge på mer funksjonalitet, blant annet ”scoreboards” for å sjekke at data du forventer, kommer, forklarer Tallaksen. Løsningen skal også ha mulighet for feilinjeksjon og overvåking. – Vi prøver å nærme oss UVM, men på en enklere måte og mer komponentorientert. I tillegg vil vi få mer styring av ”constrained random”, det vil si, påtrykke random stimuli på en strukturert måte, utdyper Tallaksen.

– ESA er ekstremt opptatt av kvalitet. Og det meldes om en del prosjekter med dårlig verifikasjonskvalitet. Både vi og ESA mener at vårt system kan bidra til å heve denne kvaliteten, understreker Tallaksen.

En annen trend forsterker dette behovet: – Man ser stadig flere lavkostprosjekter innen romindustrien, for eksempel universitetsprogrammer og billige kommunikasjonssatellitter. – På denne bakgrunn blir det enda viktigere å sikre at man unngår mer ”skrap” i verdensrommet. Da trengs det et godt system, supplerer markedsdirektør i Bitvis, William Braathen.

– Vi starter denne uken et internt prosjekt med å lage en plattform for å kunne håndtere alle enkeltelementene underveis. Det er et poeng at det blir et helhetlig system, og alt ser noenlunde likt ut selv om man utvider med mange funksjoner, sier Tallaksen.

– Løsningen skal avlaste utvikleren fra å gå i detaljer, og ikke måtte tenke ut alle feilmuligheter selv, påpeker Braathen.

– Det skal også være full funksjonell dekning, dvs. at systemet skal kunne sjekke mange statuser samtidig, fremholder Tallaksen. Full funksjonell dekning skal fange opp endringer i funksjonsdekningen ved alle endringer i designet. Da blir de også lettere å følge opp. – Selv relativt uerfarne designere skal kunne bruke dette, hevder han.

– I utgangspunktet er det komplisert nok å lage en testbenk. Det er mye å tenke på. Her får man i hvertfall en enklere start, mener Braathen. I tillegg skal det bli enklere gjenbruk, og lettere å overta designet for andre.

Det finnes selvsagt alternative verifikasjonsløsninger på markedet, men de har stort sett det til felles at de er kompliserte å bruke, og svært kostbare.

Prosjektsøknaden kom opprinnelig i stand etter en brainstorming hos Norsk Romsenter, sammen med bl.a. deltagere fra oljebransjen, med tanke på å utnytte ESA-programmer med mulighet for finansiering. Målet var å bruke erfaringer fra olje/gass til å booste norsk romvirksomhet, men det viste seg vel i stor grad at petroleumsnæringen kunne ha mer å lære fra romvirksomheten enn omvendt.

Resultatet ble uansett at Bitvis ble oppmuntret til å sende en søknad til ESA. At prosjektet i tillegg ble fullfinansiert, hører vel med til sjeldenhetene. Og konsekvensene kan bli store.

– Dette vil endre verifikasjonsmarkedet for de som driver med VHDL i dag, hevder Tallaksen. – Vi ser allerede at anerkjente rådgivere og kursholdere som Doulos nå har begynt å snakke om UVVM som én av to verifikasjonsløsninger i verden, basert på åpen kilde (den andre er OSVVM, red anm.). For å bekrefte vår ”åpen kilde” –tankegang, har vi også lagt løsningen ut på GITHUB, sier han.

Storsatsing på europeisk FPGA

I Europa, og spesielt i ESA, er det økt fokus på å gjøre seg mest mulig uavhengig av amerikansk og asiatisk teknologi, og satsingen på et europeisk FPGA-prosjekt er et godt eksempel på det.

Bitvis’ utviklingsprosjekt for et bredt anvendelig verifikasjonssystem kan også sees i sammenheng med dette.

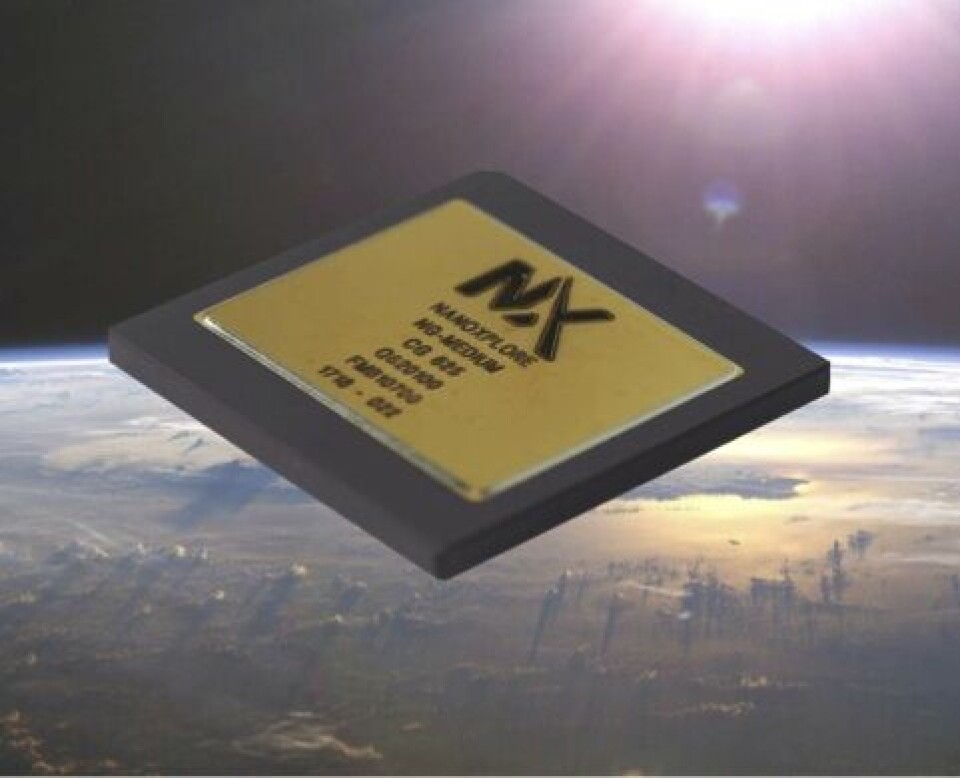

De såkalte BRAVE FPGAene skal utgjøre et konkurransedyktig europeisk alternative, og tilby høy ytelse og fleksibilitet.

Teknologien utvikles av et konsortium ledet av NanoXplore med ST Microelectronics som partner. I år har de lykkes å produsere den første BRAVE FPGA: NG-MEDIUM, en reprogrammerbar strålingsherdet FPGA i 65nm teknologi.

Det holdes et åpent gruppemøte om BRAVE FPGA i Nederland 11. september.