Verdens kraftigste DSP klarer 1600 GOPS

CEVA hevder de har verdens kraftigste DSP når de nå lanserer Gen4 CEVA-XC arkitekturen, med dynamisk rekonfigurerbar multitrådling og hastigheter på 1,8 GHz.

Denne artikkelen er 2 år eller eldre

CEVA Inc. avslørte i går de de mener er verdens kraftigste DSP-arkitektur, Gen4 CEVA-XC. Denne skal levere ekstrem ytelse for de mest komplekse parallelle prosesseringsoppgavene typisk påkrevd i 5G endepunkter og Radio Access Networks (RAN), kommersielle aksesspunkter og andre multigigabit applikasjoner med lav forsinkelse.

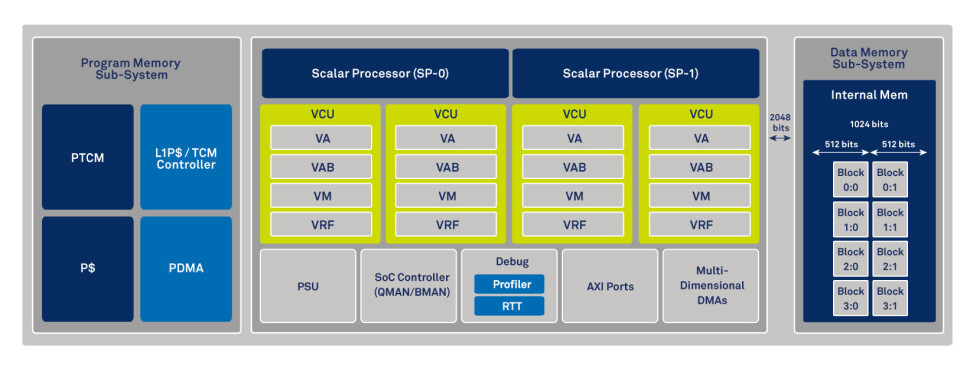

Den nye arkitekturen forener prinsippene rundt skalar- og vektorprosessering, noe som muliggjør to ganger 8-veis VLIW og opptil 14.000 bits parallellitet på datanivå.

På den 7 nm prosessnoden skal det være mulig å oppnå driftshastigheter på 1,8 GHz med bruk av en spesiell fysisk designarkitektur for en fullt syntetiserbar designflyt, og et nytt multitrådingsdesign. Dette skal tillate prosessorene å kunne rekonfigureres dynamisk som enten en vid SIMD maskin eller delt inn i mindre, samtidige SIMD tråder.

Gen4 CEVA-XC arkitekturen omfatter også et nytt minnesubsystem med 2048-bit minnebåndbredde, med koherent, tett koplet minne som støtter effektiv samtidig multitråding og minnetilgang.

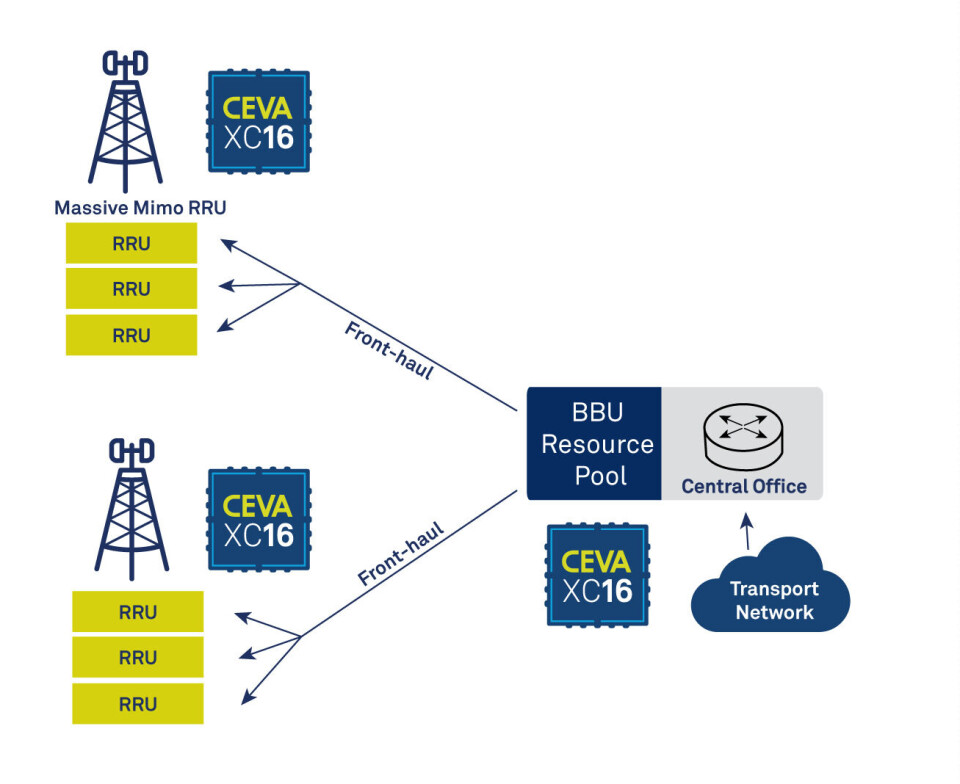

Den første prosessoren som er basert på Gen4 CEVA-XC arkitekturen er flerkjerneprosessoren CEVA-XC16, ifølge CEVA den raskeste DSPen som noen gang er laget. Den er rettet mot den raske implementeringen av ulike formfaktorer av 5G RAN arkitekturer, som Open RAN (O-RAN), Baseband Unit (BBU) aggregering samt Wi-Fi og 5G kommersielle aksespunkter.

DSPen skal også være anvendelig for massiv signalprosessering og AI-baserte arbeidsoppgaver i forbindelse med drift av basestasjoner.

Den tidligere generasjonen DSPer, CEVA-XC4500 og CEVA-XC12, driver allerede 4G og 5G mobilnett i dag, mens den nye CEVA-XC16 skal være designet inn hos en ledende nettverksleverandør for deres neste-generasjon 5G ASIC.

DSPen skal tilby parallellprosessering på opp til 1600 Giga Operations Per Second (GOPS), som kan rekonfigureres som to separate parallelle tråder. Disse skal kunne kjøre samtidig, mens de deler deres L1 Data minne med cachekoherens, noe som spesielt forbedrer forsinkelse og effektivitet for kontrollprosessering av PHY, uten behov for en ekstra CPU.