Leverer første 10nm FPGA

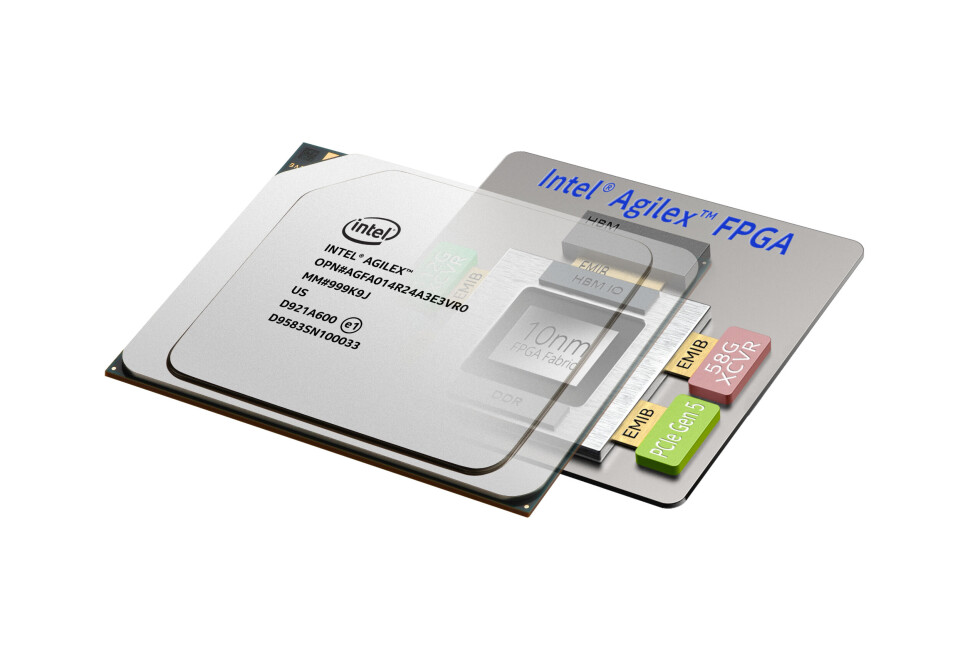

Intel har startet utskiping av de første Agilex-FPGAene i deres 10nm prosessteknologi.

Denne artikkelen er 2 år eller eldre

Intel Agilex skal ha en ytelse som er opp til 40% høyere enn Stratix 10, og skal være den eneste FPGA som støtter herdet BFLOAT16, med opp til 40 teraflops DSP- (digital signalprosessor) ytelse.

Partnere i selskapets pilotprogram – blant annet Colorado Engineering Inc., Mantaro Networks, Microsoft og Silicom – har nå fått tilgang til de nye 10nm komponentene, som skal brukes til utvikling av avanserte nettverksløsninger, 5G og rask dataanalyse.

– Produktfamilien Agilex utnytter bredden i Intels innovasjon og teknologiledelse, inkludert arkitektur, pakking, prosessteknologi, utviklingsverktøy samt en snarvei til effektreduksjon med eASIC-teknologien, sier leder for nettverks- og kundespesifiserte logikk hos Intel, Dan McNamara.

– Dette muliggjør nye nivåer av heterogen dataprosessering, systemintegrasjon og prosessorkommunikasjon, og serien vil være de første 10nm FPGA som tilbyr cache-koherent kommunikasjon med lav forsinkelse til Intel Xeon-prosessorer, med den nye, kommende Compute Express Link (CXL), fremholder han.

Intel Agilex-familien kombinerer flere nye Intel-teknologier, inkludert andre generasjon HyperFlex FPGA-matrise bygget på selskapets 10nm prosess, og heterogen 3D silisium-i-pakke (SiP) teknologi, basert på Intels velprøvde sammenkoblingsbro for innvevde flerkjerne (EMIB). Intel kan dermed integrere ulike «fliser» («tiles») i form av analogt minne, kundespesifiserte prosessering, kundespesifiserte I/O og Intel eASIC i én enkelt pakke sammen med FPGA-matrisen. Det skal også være en logisk vei for å migrere FPGA-design til strukturerte ASIC (kundespesifiserte integrerte kretser).

Løsningen støtter PCIe Gen 5, opp til 112 Gbps transceivere og har støtte for eksisterende DDR4, samt kommende DDR5, HBM og Intel Optane DC-persistent minne.