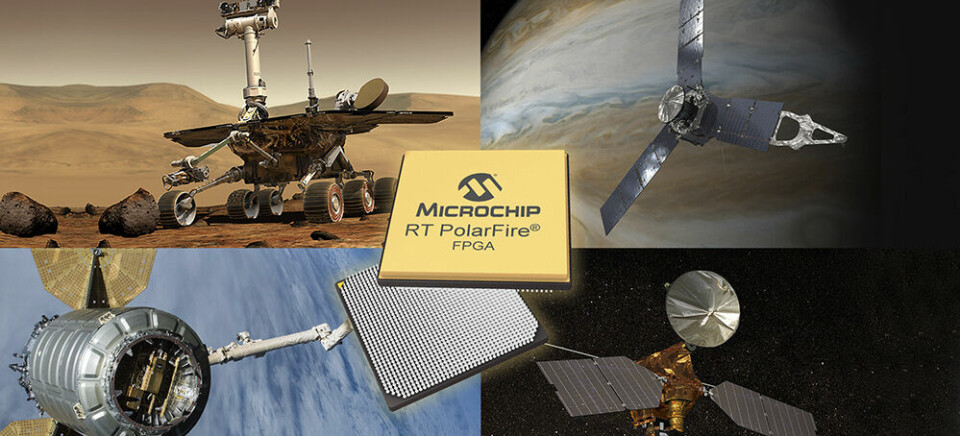

FPGA for romfart

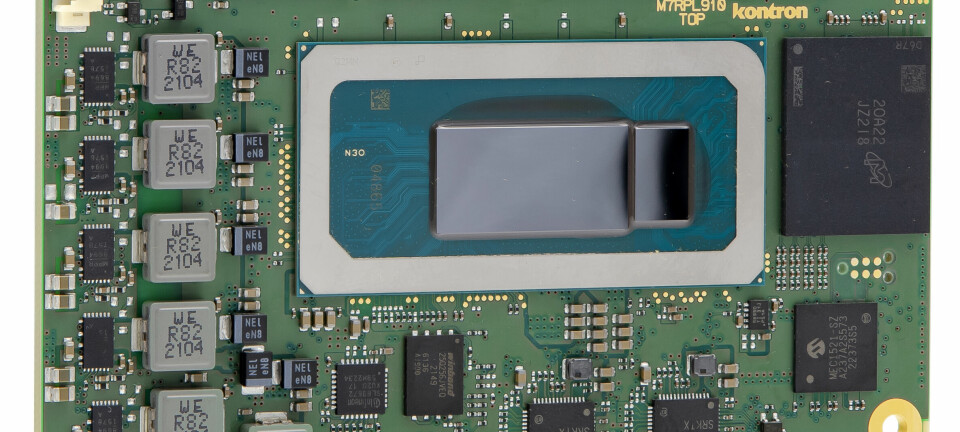

Microchip lanserer RT PolarFire FPGA, optimalisert for å møte krav fra nyttelastsystemer i romfartøy og høyhastighets datalinjer, med lavest mulig effektforbruk og varmeutvikling. Den nye FPGAen bygger på Microchips tidligere RTG4 FPGA.

Denne artikkelen er 2 år eller eldre

Ingeniører som utvikler romfartselektronikk anvender strålingstolerante (Radiation Tolerant – RT) feltprogrammerbare portmatriser (Field Programmable Gate Arrays – FPGA) for å lage systemer ombord som møter krevende ytelsesbehov til fremtidige romekspedisjoner, overleve den brutale oppskytingssekvensen og fortsetter å fungere pålitelig i det tøffe rommiljøet. Microchip har utvidet deres RT FPGA-tilbud for å gjøre disse egenskapene tilgjengelig for høy-ytelses romfartsapplikasjoner.

Et økende antall romfartsapplikasjoner trenger stadig mer prosesseringsytelse, slik at de kan sende prosessert informasjon fremfor rådata, og dermed utnytte den begrensede nedlastingskapasiteten optimalt. Den nye RT PolarFire FPGA gjør dette mulig til en betydelig lavere kostnad og med raskere designsykluser enn hva som er mulig med kundespesifiserte kretser (Application-Specific Integrated Circuits – ASIC), lover leverandøren.

Den reduserer dessuten effektbehovet betydelig, sammenlignet med alternativet med å bruke FPGAer basert på SRAM (Static Random Access Memory), samtidig som de reduserer sårbarheten overfor strålingsindusert konfigurasjonspåvirkning. RT PolarFire FPGA støttes opp av all nødvendig strålingsdata, spesifikasjoner, pakkedetaljer og verktøy som trengs for å starte nye design umiddelbart.

Den nye FPGAen bygger på Microchips RTG4 FPGA, som er i bruk i romfartsapplikasjoner som krever den innebygde strålingstoleransen mot Single Event Upsets (SEUs) og ikke minst den naturlige immuniteten mot Single Event Latch-ups (SELs) og konfigurasjonspåvirkning. For romfartsapplikasjoner som krever opp til fem ganger prosesseringskapasiteten, kan RT PolarFire FPGA tilby 50 prosent ytelse og tre ganger logiske elementer og Serialiser-Deserialiser (SERDES) båndbredde. Den kan også tilby seks ganger så mye innvevd SRAM, for å kunne muliggjøre større systemkompleksitet enn det som tidligere har vært mulig med bruk av FPGA, og tåler Total Ionising Dose (TID) eksponering utover de 100 kilorads (kRads) som er typisk for de fleste satellitter i jordbane, og for mange ekspedisjoner i det ytre rom.

Dessuten er effektforbruket redusert til omkring halvparten av det i alternative SRAM-baserte FPGAer med tilsvarende tetthet og ytelse. Dens SONOS Non-Volatile (NV) teknologi betyr at konfigurasjonssvitsjene kan implementeres i en mer energieffektiv arkitektur som kutter utviklingstid og materialkostnader gjennom forenklet, mindre kostbar og lettere kraftsystemdesign, samtidig som varmeutviklingen minimaliseres for å redusere problemene med termisk styring. Designene blir ytterligere forenklet, sammenlignet med bruk av SRAM-baserte FPGAer, ettersom RT PolarFire FPGA eliminerer kostnader, kompleksitet og nedetid for å bøte på konfigurasjons-SEU.

FPGAen vil gjennomgå standardprosessene for å oppfylle QML-standarder inkludert klasse V kvalifisering for svært kritiske applikasjoner.

Pakket i en hermetisk forseglet portmatrise med keramiske kolonner med integrerte avkoplingskondensatorer, vil Microchips RT PolarFire RTPF500T FPGA være tilgjengelig og kvalifisert for implementering i romferder i 2021. Kunder kan starte opp design allerede nå ved hjelp av den kommersielle PolarFire MPF500T FPGA med Microchips Libero programvareverktøy, som inkluderer opsjon for Triple Mode Redundancy (TMR) syntesestøtte med tanke på implementering av SEU-avbøting der det trengs, slik som i styrekretser.

Utviklingskort er tilgjengelige med den kommersielle PolarFire FPGA og vil senere inkludere RT PolarFire komponenten i form av en utviklingsmodell.

Tilgjengelige strålingsdata omfatter TID, SEL, konfigurasjonsupsets, og upsets i ubeskyttet D-Flip Flop (DFF) og minne.