RISC-V muliggjør innovasjon innen prosessorarkitektur for SoC FPGA

Prosessorarkitekturen RISC-V har lenge vært en het potet blant de store halvlederleverandørene. Vi utfordret Microchips Tim Morin på hvorfor de nå går for RISC-V. Her er hans kommentar.

Denne artikkelen er 2 år eller eldre

Hos Microchip er det ikke instruksjonssettarkitekturen (ISA) eller brikken som betyr noe, men vår evne til å støtte prosesseringsbehovene til en bred kundebase – som strekker seg over et stort spekter av applikasjoner og markeder. Tross alt byr vi på PIC-, AVR-, ARM-, MIPS-, og nå RISC-V brikker og utviklingsverktøy til våre kunder, og tilbyr masser av muligheter å velge mellom.

SoC FPGA

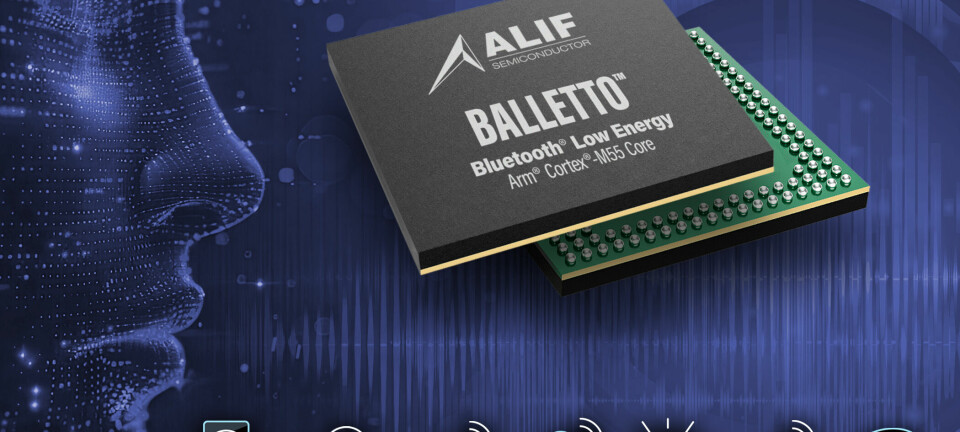

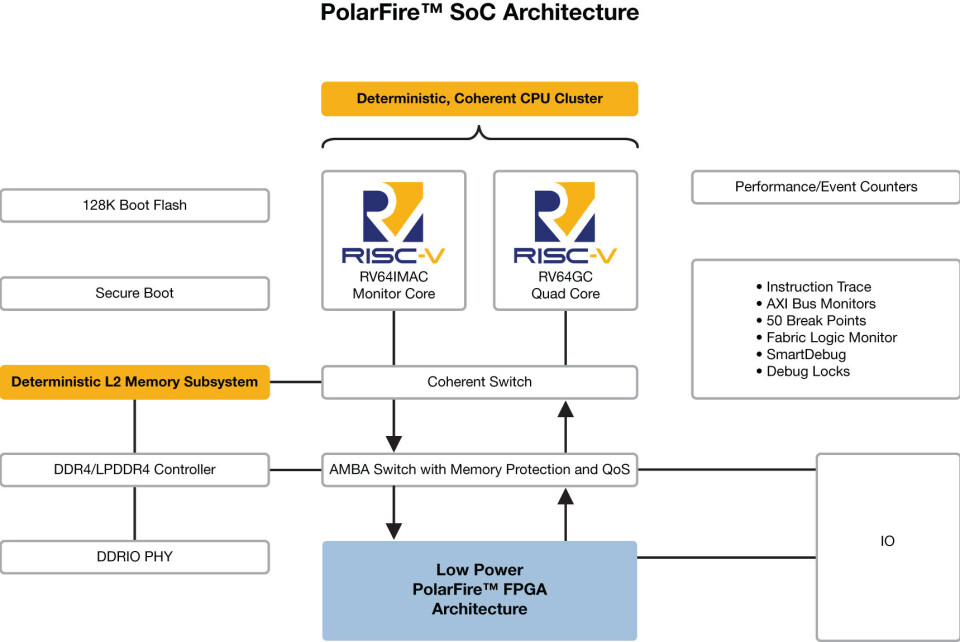

For vår neste generasjon FPGA (Field Programmable Gate Arrays) som integrerer et prosessorsubsystem, slik som en ASIC (Application Specific Integrated Circuit) blokk, velger vi RISC-V ISA fremfor andre kommersielt tilgjengelige arkitekturer, primært fordi den tjener våre sluttmarkeder på en mer effektiv måte både for oss og kundene. Dette er våre høysikkerhets, mellomstore System-on-Chip (SoC) FPGAer som har stor utbredelse i alle markedssegmenter unntatt mobil.

Abstraherer arkitekturen

Som sådan, har SoC FPGAer varierende applikasjonskrav, avhengig av disse sluttmarkedene. Når det gjelder vår nylig lanserte PolarFire SoC bestemte vi oss for å bringe til markeds en mellomklasse, laveffekt SoC FPGA, i stand til å kjøre et rikt OS slik som Linux. Med en gang du bestemmer deg for å støtte et rikt OS er du effektivt abstrahert vekk fra applikasjonsprogramutvikleren, det underliggende ISA og mikroarkitektur. Det er riktig at ISA i kombinasjon med mikroarkitekturen vil levere måltall for effekt, ytelse og areal (Power, Performance, and Area – PPA) for en gitt applikasjon, men for applikasjonsprogramutvikleren administrerer du i stor grad prosessering, I/O og minne. Likevel vil noen si "Hva med økosystemet?". "Det er så mye der ute for visse ISA".

"Modne" ISA og økosystem?

Sant nok, det forventer en jo av modne ISA. Men, en må huske at det knapt fins to systembrikker i markedet med samme minnekart, I/O, bussvitsj, minnekontroller, oppstartsprosess osv. Alle leverandører designer og produserer ting for å oppfylle kundenes behov, og ikke alle kunder har samme behov. Økosystemene er fragmenterte, og du må porte fra leverandør A til leverandør B, selv innenfor det samme ISA. Dette vil aldri endre seg. Dette er et viktig motiv for OEMs til å gå over til et rikt operativsystem (OS) og abstrahere vekk den underliggende silisiumen, ettersom alle SoCer er forskjellige! Når programvareingeniørene er maskinvareingeniørene tallmessig overlegne i forholdet 10:1, vil selskapene utnytte deres programvareutvikling så mye som mulig.

Bedre valg

Beslutningen om å støtte et rikt OS tillot oss å vurdere hvilken prosessor-IP som var tilgjengelig i markedet i forhold til våre kunders krav, samtidig som vi visste at OS'et til slutt abstraherer alt sammen bort uansett, unntatt når det gjelder PPA selvsagt, hvilket er årsaken til at vi valgte RISC-V.

Innovere på arkitekturnivå

RISC-V gjør oss i stand til å innovere på arkitekturmessig nivå, helt gratis. Det gjør våre kunder i stand til å påvirke vår mikroarkitektur på måter de tidligere ikke trodde var mulig, slik at de kan utvikle anvendelsesrettede design for applikasjoner som bildebehandling og maskinlæring, sikkerhetskritiske systemer, industriell IoT, sikker kommunikasjon, og våpensystemer. I PolarFire SoC, for eksempel, konstruerte vi i samarbeid med vår IP-partner SiFive et 5-kjerne prosessorsubsystem som kan kjøre harde sanntidsapplikasjoner og SMP Linux med en koherent meldingsformidlingsrutine, alt i den samme prosessoren, med bruk av det samme ISA. Hvordan vi gjorde det?

Viktige endringer

Det begynner med kravene kundene stiller for å kunne styre en maskin deterministisk, og utnytte økosystemet for Linux i stadig mindre maskiner som har enten termiske- eller laveffekt begrensninger. Noen relativt enkle endringer fra en eksisterende CPU-spesifikasjon tillot oss å gjøre dette. Endringer omfatter blant annet:

- Å gi brukerne evnen til å kunne konvertere deler av L1 minne-subsystemet til et tett integrert minne, uten å miste noe og med direkte tilgang

- Å gi brukerne evnen til å skru av grenforutsigere (branch predictors) på enhver kjerne.

- Tillate brukerne å partisjonere L2 minne-subsystemet til et såkalt Loosely Integrated Memory (LIM). Et LIM kan gis pinneforbindelse til en prosessor, for deterministisk tilgang.

Sluttresultatet er at PolarFire SoC ivaretar kundene med en innovativ SoC FPGA, basert på RISC-V arkitekturen, som tillater dem å sette sammen harde sanntidsapplikasjoner og Linux i én enkelt brikke, for å kunne implementere laveffekt, sikre og pålitelige design.

Denne artikkelen stod første gang på trykk i Elektronikk nr. 5 2019