Toshiba velger Tensilica

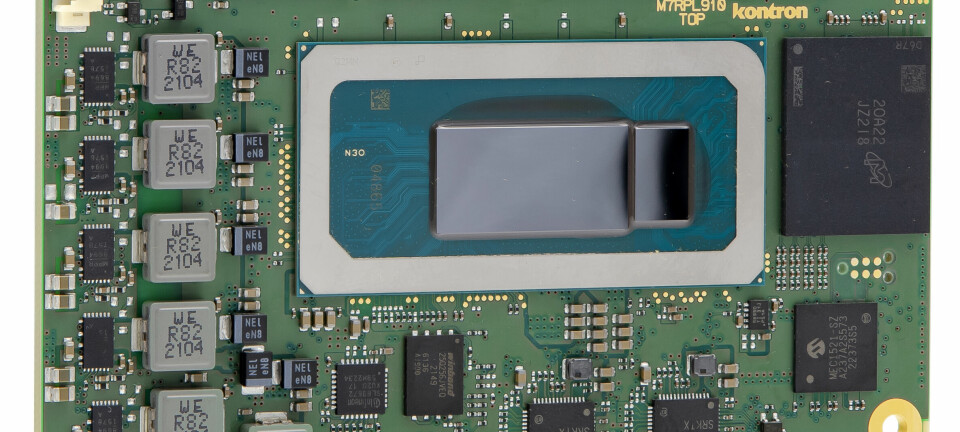

Cadence Design Systems melder at Toshiba har implementert Cadence Tensilica Vision P6 DSP for sin neste generasjons systembrikke (SoC) rettet mot bilindustrien.

Denne artikkelen er 2 år eller eldre

Vision P6 DSP skal gi opptil 3,8 x mer energieffektivitet enn CPUer alene og klarer 1024 giga-operasjoner (GOPS). Det gjør at den fungerer som en avlastningsprosessor for visjons- og AI-oppgaver.

I tillegg har Toshiba har integrert «Cadence Xtensa Imaging Library» (Xi-Lib) i sitt programvareutviklingssett (SDK), slik at man får tilgang til signalprosessoren for å tilpasse algoritmer, for eksempel. I tillegg er Vision P6 DSP’s kjerne, utviklingsverktøy og biblioteker designet for å gjøre det mulig for SoC-leverandører å oppnå «ISO 26262 automotive safety integrity level D»-sertifisering.

Vision P6 DSP støtter også AI-programmer utviklet i Caffe og TensorFlow gjennom Tensilica Neural Network Compiler (XNNC). Kompilatoren kartlegger nevrale nettverk (NN) til kjørbar og høyoptimalisert høyytelseskode for Vision P6 DSP. Den støtter også API for Android Neural Network (ANN) for AI-akselerasjon på enheter i Android-drevet utsyr.