Laveffekt PCI Express Gen 4 buffere

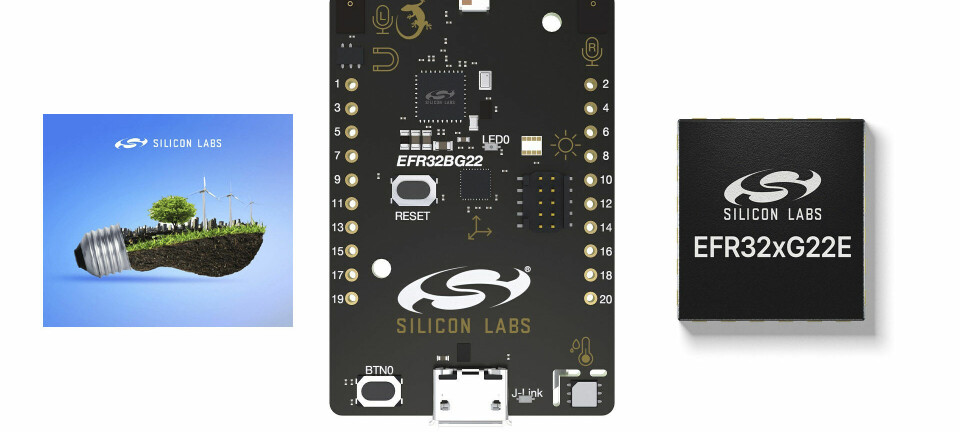

En ny bufferfamilie fra Silabs skal være den første som tilbyr en PCIe Gen 4-kompatibel løsning for laveffekt 1,5 V/1,8 V anvendelser.

Denne artikkelen er 2 år eller eldre

Silicon Labs (Silabs) har lansert en ny familie med laveffekt PCI Express (PCIe) Gen 1/2/3/4 klokkebuffere som skal gi klokkedistribusjon med ultra-lav jitter clock i 1,5 V og 1,8 V applikasjoner. Med additiv jitterytelse på 40 fs RMS (typisk), kan Silabs nye Si532xx PCIe klokkebuffere gi mer en 90 prosents margin til de strenge jitterspesifikasjonene for PCIe Gen 3 og Gen 4, og dermed forenkle klokkedistribusjon og senke risiko under produktutvikling, melder selskapet.

I økende grad bruker for eksempel utstyr i datasentre, inkludert grensesnittkort for nettverk (NIC), PCIe buss-utvidere og høy-ytelses databehandlings- (HPC) akseleratorer laveffekt 1,5 V eller 1,8 V forsuninger til å redusere det totale effektforbruket.

De nye bufferkretsene drives av en enkel 1,5 V - 1,8 V forsyning og har opptil 12 klokkeutganger. De støtter PCIe Common Clock, Separate Reference No Spread (SRNS) og Separate Reference Independent Spread (SRIS) arkitekturer, og kan dermed brukes i et stort spekter av anvendelser. Si532xx-klokker er non-PLL-baserte fan out buffere, som støtter distribusjon av spredt-spektrum klokkesignaler, uten å påvirke signalintegriteten.

Det er mulig å kaskadekoble flere buffere, og fortsatt møte maksimalt tillat jitterbudsjett for systemet, på 0,5 ps RMS.

Enhetsdriverne på utgangene i Si532xx utnytter Silicon Labs’ push-pull HCSL teknologi, som skal eliminere behovet for eksterne termineringsmotstander, som er påkrevd i konvensjonelle PCIe buffere som anvender konstant-strøm utgangsdriverteknologi.