Samsung går for 4nm

Samsung har avslørt detaljer om hvor veien går for fremtidens halvlederprosesser. Nå skal de utfordre Moores lov!

Denne artikkelen er 2 år eller eldre

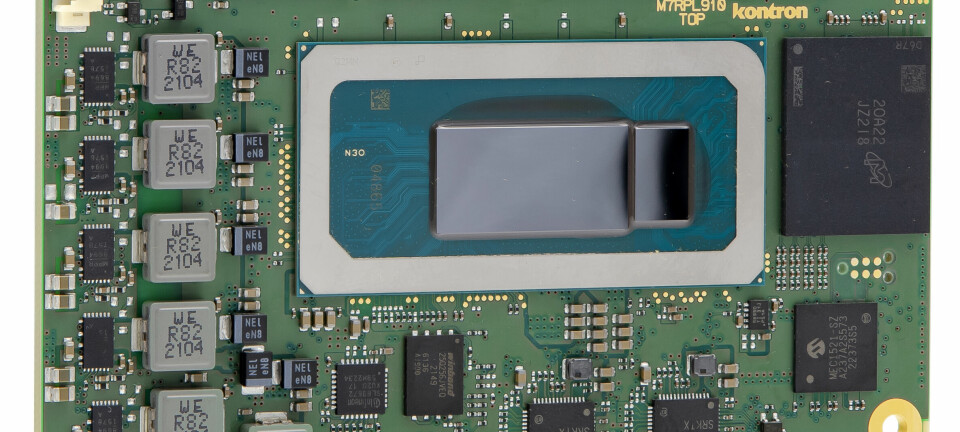

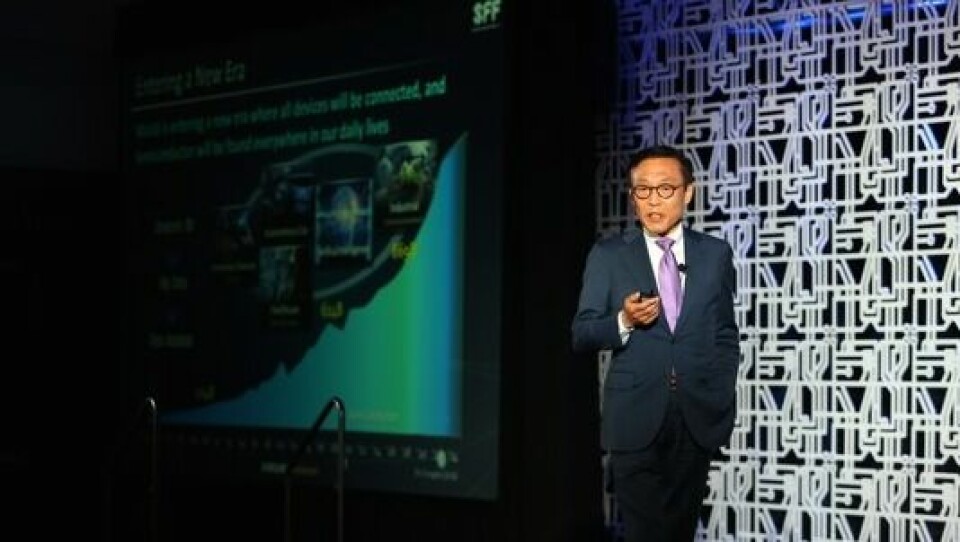

Samsung Electronics Co., Ltd. kunne sist fredag presentere et omfattende veikart for nye silisiumprosesser for å produsere raskere og mer energieffektive brikker.

Selskapet har til hensikt å lede an innen henholdsvis 8nm, 7nm, 6nm, 5nm, 4nm og 18nm FD-SOI i tiden fremover.

Under sitt årlige Samsung Foundry Forum lanserte de følgende teknologier:

· 8LPP (8nm Low Power Plus): 8LPP skal gi de mest omfattende skaleringsmulighetene før man går over til EUV (Extreme Ultra Violet) litografi. Denne kombinerer viktige innovasjoner fra Samsungs 10nm teknologi, og 8LPP vil tilby flere fordeler når det gjelder ytelse og porttetthet, sammenlignet med 10LPP.

· 7LPP (7nm Low Power Plus): 7LPP vil bli den første halvlederprosessen som benytter en EUV litografiløsning. 250W maks EUV kildeeffekt, som er den viktigste milepælen for å sette EUV i høyvolum produksjon, ble utviklet i samarbeid mellom Samsung og ASML. EUV litografi kan bryte grensene til Moores lov om skalering, og baner veien for halvledergenerasjoner på en enkelt nanometer.

· 6LPP (6nm Low Power Plus): 6LPP vil ta i bruk Samsungs spesielle Smart Scaling løsninger, som vil bli implementert på toppen av den EUV-baserte 7LPP teknologien, og tillater større arealer og ultra-laveffekt.

· 5LPP (5nm Low Power Plus): 5LPP utvider de fysiske skaleringsbegrensningene i FinFET strukturer, ved å implementere teknologiinnovasjoner fra den neste generasjonen, 4LPP, for bedre skalering og effektreduksjon.

· 4LPP (4nm Low Power Plus): 4LPP vil bli den første implementeringen av neste generasjon komponentarkitektur – MBCFETTM struktur (Multi Bridge Channel FET). MBCFETTM er Samsungs egenutviklede GAAFET (Gate All Around FET) teknologi, som anvender en Nanosheet komponent for å overvinne begrensningene for fysisk skalering og ytelser knyttet til FinFET arkitekturen.

· FD-SOI (Fully Depleted – Silicon on Insulator): Med tanke på spesielt IoT applikasjoner, vil Samsung gradvis utvide sin 28FDS til et bredere plattformtilbud ved å integrere muligheter for RF (radiofrekvens) og eMRAM(embedded Magnetic Random Access Memory). 18FDS er neste generasjons node på Samsungs FD-SOI veikart, med forbedret PPA (Power/Performance/Area).