Maskinlæring og partiell rekonfigurering

FPGA Forum 2017 er i full gang. Årets program har overraskende mye fokus på maskinlæring og partiell rekonfigurering.

Denne artikkelen er 2 år eller eldre

Dynamisk partiell rekonfigurering, der en del av FPGAen kan endre funksjon samtidig som andre deler av komponenten utfører rutineoppgaver, var mye omtalt for noen år siden, men ble i stor grad betraktet som en akademisk øvelse.

Flere foredragsholdere og utstillere på FPGA Forum i Trondheim (15.-16. Februar) har imidlertid trukket teknologien frem igjen. Jan Anders Mathisen fra Avnet Silica (Xilinx) er en av dem som ønsker å gi partiell rekonfigurering et puff fremover.

– Det er ikke lenger snakk om ”eksotiske” design. Partiell rekonfigurering har mange fordeler. I tillegg har vi nå full støtte for denne metoden i utviklingsverktøyet Vivado, sier han.

Blant annet Kongsberg Defence Systems delte sine erfaringer med bruk av partiell rekonfigurering under konferansen.

Maskinlæring og nevrale nettverk er et annet gjennomgående tema. – FPGA er godt egnet for massiv parallellprosessering. Nå ser vi også fremveksten av en ”killer app” å bruke dette til – nemlig maskinlæring, sa Xilinx-guruen Liam Madden i sitt innledningsforedrag. Behovet for regnekraft i fremtidige applikasjoner innen for eksempel 5G og virtuell virkelighet kan drive dette. Nye fremskritt innen bygging av nevrale nettverk og ”dyp læring” er interessante aspekter i FPGA-verdenen.

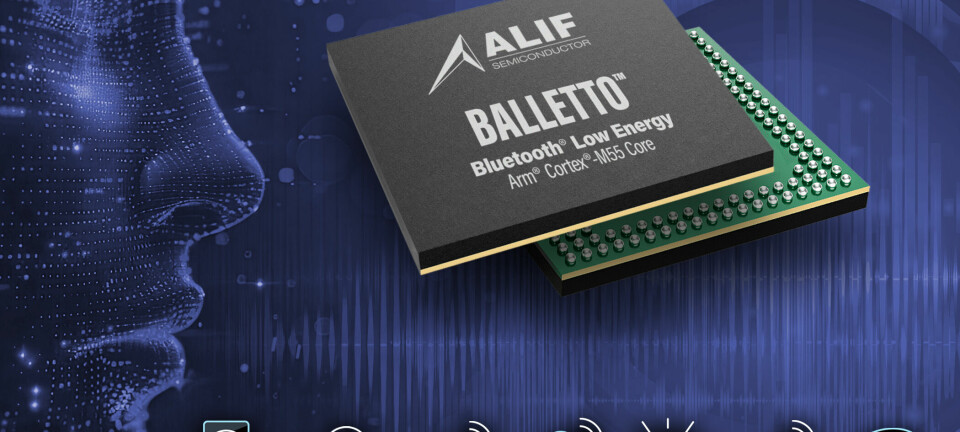

– IoT, autonome systemer som selvkjørende biler osv. genererer enorme mengder data som skal brukes som beslutningsgrunnlag i ulike situasjoner. Datamengden er et problem i den grad at mest mulig må håndteres ”lokalt”, nærmest mulig sensorer osv., sier Nikolay Rognlien i Arrow (Altera/Intel PSG).

– Skal man løse ting med maskinlæring og nevrale nettverk, vil markedene kreve at løsningene er skalerbare. FPGA har tradisjonelt hatt en plass i hele kjeden fra sensor via nettverk og gateway til sky- og serverløsninger, og tilbyr denne skalerbarheten, sier han.

Kognitive nevrale nettverk (CNN) vil komme, og Intel PSG har strategier for å møte utfordringene dette vil innebære, hevder Rognlien.

Mer om FPGA Forum 2017, maskinlæring, partiell rekonfigurering og programmerbare teknologier i Elektronikk nr 3 (Mars) 2017.