Fagartikkel: ASIC – en løsning med lav kostnad og lav risiko!

Ja, du leste riktig. Gjennom årene har vi lært at ASIC er blitt dyrere og dyrere, og nærmest er blitt forbeholdt multi-million dollarprosjekter. Men: nå har noe endret seg.

Denne artikkelen er 2 år eller eldre

Når du ser på de mange artiklene som omhandler de stadig økende kostnadene ved utvikling av halvlederkomponenter, er det naturlig å tenke at bare et ekslusivt utvalg av velfinansierte oppstartsbedrifter, store systemselskaper eller komponentleverandører vil ha råd til å utnytte de mange tekniske og kommersielle fordelene ved å ta i bruk applikasjonsspesifikke integrerte kretser (ASICs). Men faktisk, med et bredt utvalg av rimelige designverktøy og enkel tilgang til fleksible, modne IC-prosesser, kunne det knapt vært et bedre tidspunkt å utforske fordelene ved en ASIC.

Myter for fall

Når det sirkulerer tall som over 25 millioner USD bare for å kjøpe ett maskesett, og designkostnader som når opp i tresifrede millionbeløp (USD), får man inntrykk av at ASIC-design er den rike manns privilegium. Men det er verdt å merke seg at disse tallene kun gjelder de ypperste, ledende prosessene som bare er kostnadssvarende i forbindelse med store systembrikker (SoC) i høyvolum forbrukerprodukter som PCer og smarttelefoner. For applikasjoner som Tingenes Internett (IoT), der integrasjons nivåene er lavere, og behovet for å kommunisere med ”den virkelige verden” krever bruk av analoge kretser, er modne, “More than Moore” prosessteknologier bedre egnet. Her er kostnadene og risiko ved å ta i bruk ASIC-teknologi helt annerledes.

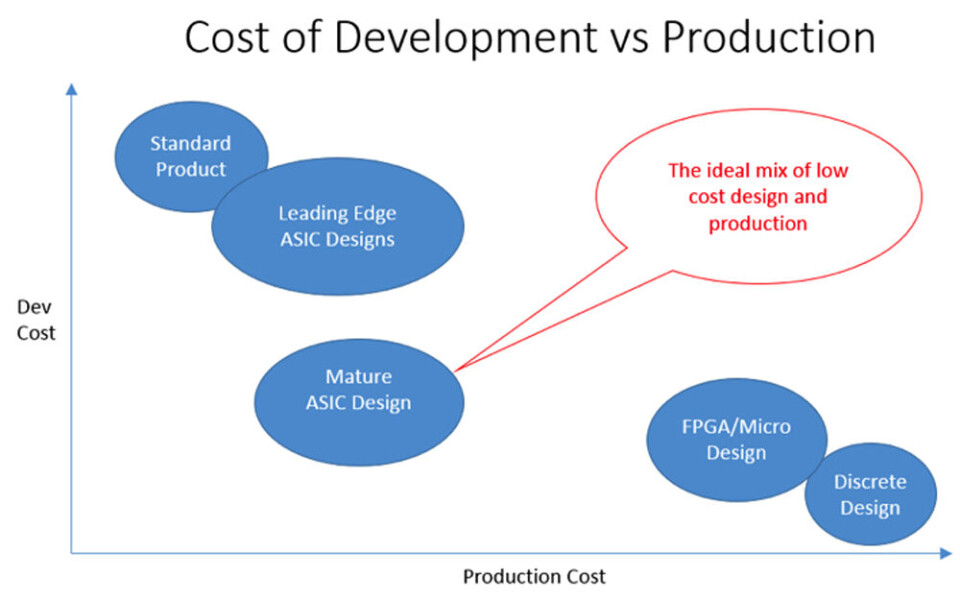

Til tross for hypen rundt økende kostnader, har design og produksjon av ASIC faktisk blitt billigere for mange prosjekter. Og det i en slik grad at mange mennesker som trodde at feltprogrammerbare portmatriser (FPGA) eller mikrokontrollere sammen med diskrete analoge komponenter var deres eneste muligheter, nå finner ut at en dedikert ASIC-tilnærming er mer kosteffektiv. Nøkkelen ligger i å velge riktige designverktøy og ikke minst prosessteknologi, slik at man kan dra nytte av moden teknologi for å oppnå kostnadsbesparelser, og sikre god tilgjengelighet av gratis eller rimelig IP (intellektuell eiendom). Figuren under viser de relative utviklings- og produksjonskostnadene for standard IC produkter, ASIC og rekonfigurerbare komponenter som FPGA.

Fordelen ved ASIC

ASIC har en hel rekke andre viktige fordeler, utover rimelig produksjon. ASIC kan by på større ytelse, lavere effekt, høyere spenninger, redusert fotavtrykk/materialkostnad og dermed bedre pålitelighet. Imidlertid er noe av det viktigste ASIC kan tilby i dagens situasjon, høyere IP-sikkerhet, ettersom en ASIC er mye vanskeligere å gjøre konstruksjonsgransking (reverse engineering) på, enn et mikrokontroller- eller FPGA-design, der IP er lagret i et vanligvis enkel avlesbart minne.

Oppsiden ved modne prosesser

Produksjonskostnadene i de mer modne nodene faller over tid, etter hvert som fabrikken blir nedbetalt, og fabrikkeieren bare trenger å dekke løpende kostnader som bemanning og materialer. En teknologi som den stadig populære 0,18um mikset-signal CMOS noden har vært på banen siden begynnelsen av 90-tallet, så alle fasiliteter og utstyrskostnader er for lengst godt og vel avskrevet.

I likhet med produksjonskostnadene, har designkostnadene for de som arbeider innen de modne nodene også forbedret seg, spesielt for de som jobber med blandede signalveier. Det meste av risikoen innen analoge IC-design ligger i usikkerhet. Når prosessene først rulles ut, utgjør de et bevegelig mål for analogdesigneren. Viktige prosessparametere kan endres dramatisk fra batch til batch ettersom ingeniørene i silisiumsmien skviser oppsettet for stadig å forbedre den totale yielden. Dette gjør det vanskelig å modellere analoge kretser. Men så snart prosessen er optimalisert, kan silisiumsmien gjøre tilgjengelig nøyaktige bibliotek som bedre reflekterer den oppførselen utviklerne vil se i virkelig silisium, og dermed reduseres designrisikoen. Disse forbedringene realiseres i fabrikkspesifikke prosessdesignsett, eller PDK. Disse er det fabrikkene selv som tilbyr, og jo mer de brukes, jo bedre blir de.

Høy tilgjengelighet av gjenbrukbar IP

Dessuten tilbyr mange fabrikker med modne mikset-signal prosesser også et stort spekter av forhåndskarakterisert IP. Bruken av slike IP-blokker er vanlig i den digitale verden, der ledende selskaper som ARM og Imagination Technologies tilbyr en bred portefølje av funksjonsblokker slik som mikrokontrollere – hvorav mange er egnet for bruk i disse miksede teknologiene, i applikasjoner som Tingenes Internett. Analoge kretsblokker som komparatorer, operasjonsforsterkere, bandgap, analog-til-digital- og digital-til-analog-omformere bidrar i betydelig grad til å redusere utviklingstid og risiko for designeren.

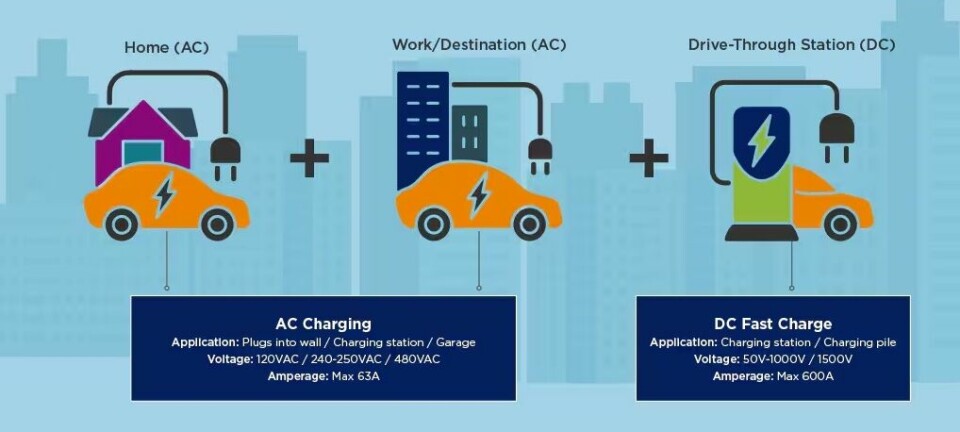

Disse eldre prosessene tilbyr også støtte for høyere driftsspenninger, hvilket betyr at de er vanlige valg for mikset-signal design der den analoge nøyaktigheten er viktig, eller der det er behov for å fungere med eller styre høyere spenninger, som for eksempel innen bil-, industristyrings- eller kraftstyringsapplikasjoner.

Enkelte silisiumsmier kan til og med skreddersy sine prosesser til å møte spesifikke produkt- eller applikasjonskrav. Britiske Plessey, for eksempel, har en unik laveffekt prosess som er spesielt utviklet for implanterbare medisinske enheter, som pacemakere, der batterilevetiden ikke bare er viktig, den kan bety liv eller død!

Deling av kostnadene

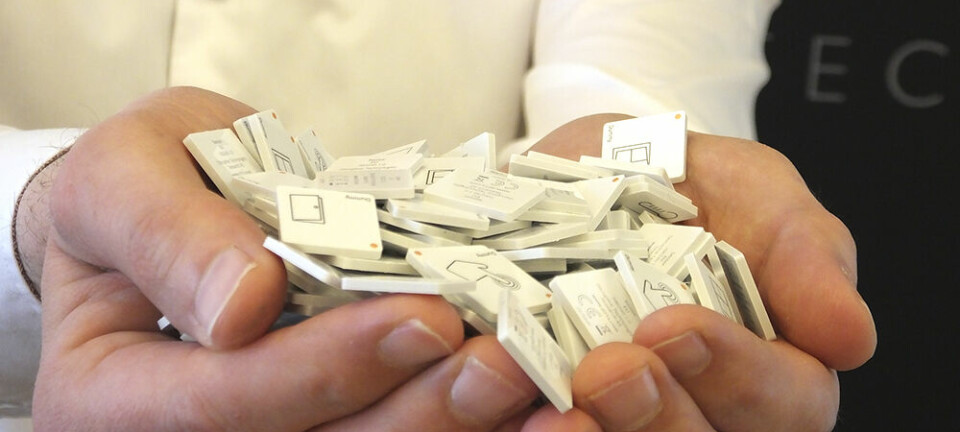

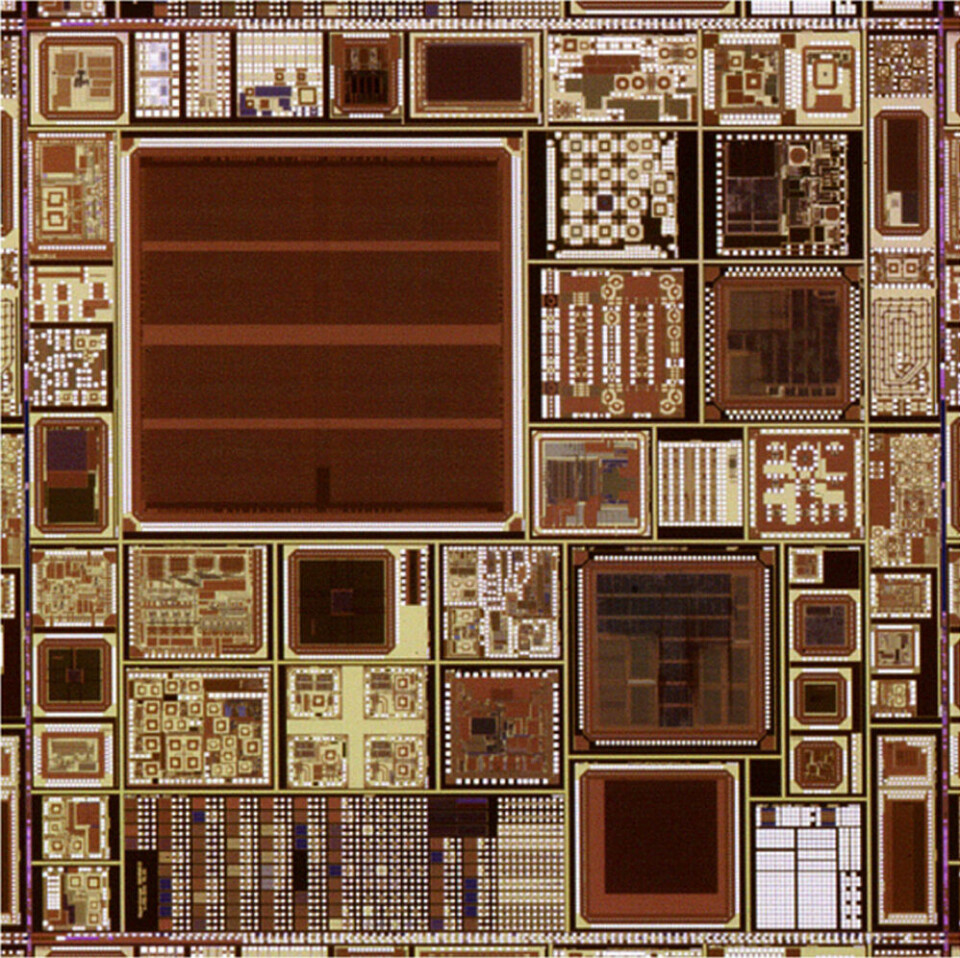

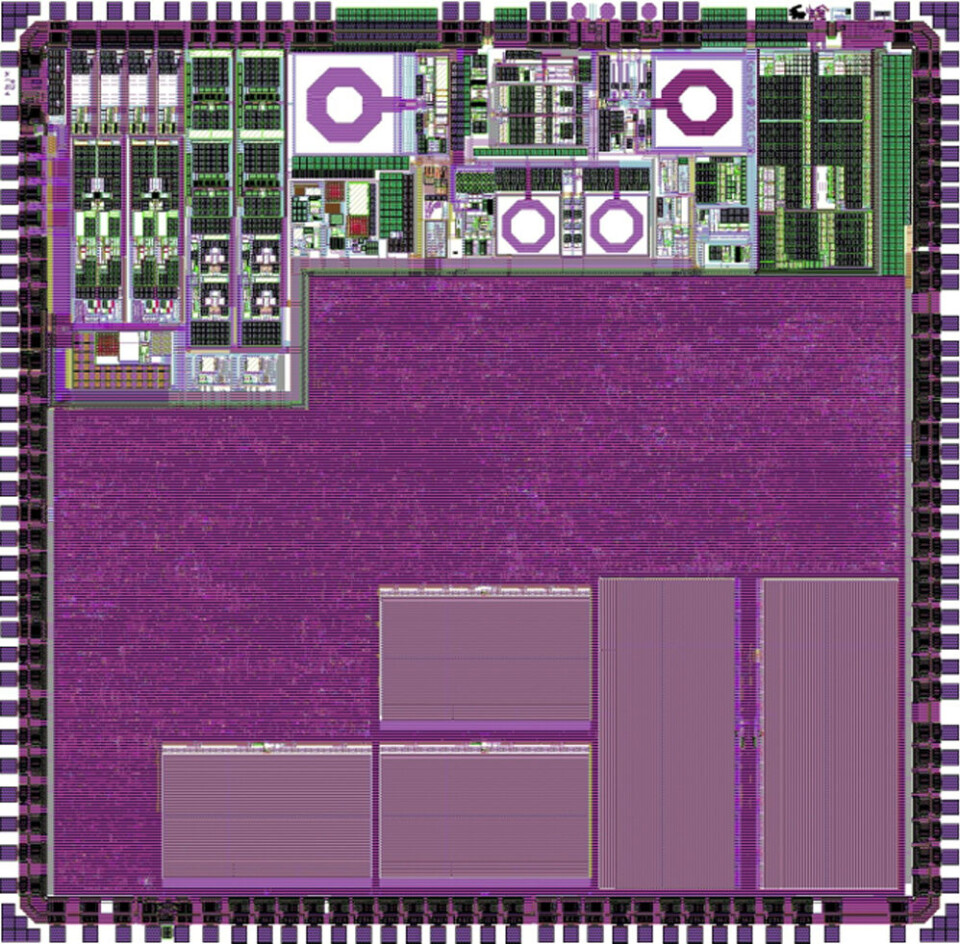

Kostnader og risiko knyttet til masker og produksjon av silisiumskiver kan reduseres ytterligere ved å benytte tjenester der flere prosjekter deler en skive; multi-project wafer (MPW) fra organisasjoner som for eksempel Europractice. Der det er behov for mindre antall brikker for evaluering og kvalifisering, eller små produksjonsserier, kan flere designintegreres i et enkelt maskesett, som vist i Figur 2 (kilde: MOSIS). Kunder kan typisk bestille 40 komponenter for evaluering før de investerer i et eget maskesett, men opp til 1000 komponenter av ethvert design kan produseres i en enkelt MPW kjøring. Kostnadene for MPW er bare en brøkdel sammenlignet med kostnaden for et komplett sett med dedikerte masker og skiver, ettersom kundene bare betaler for den delen av skiven som deres komponenter okkuperer. De fleste større silisiumsmier tilbyr multiprosjektskiver.

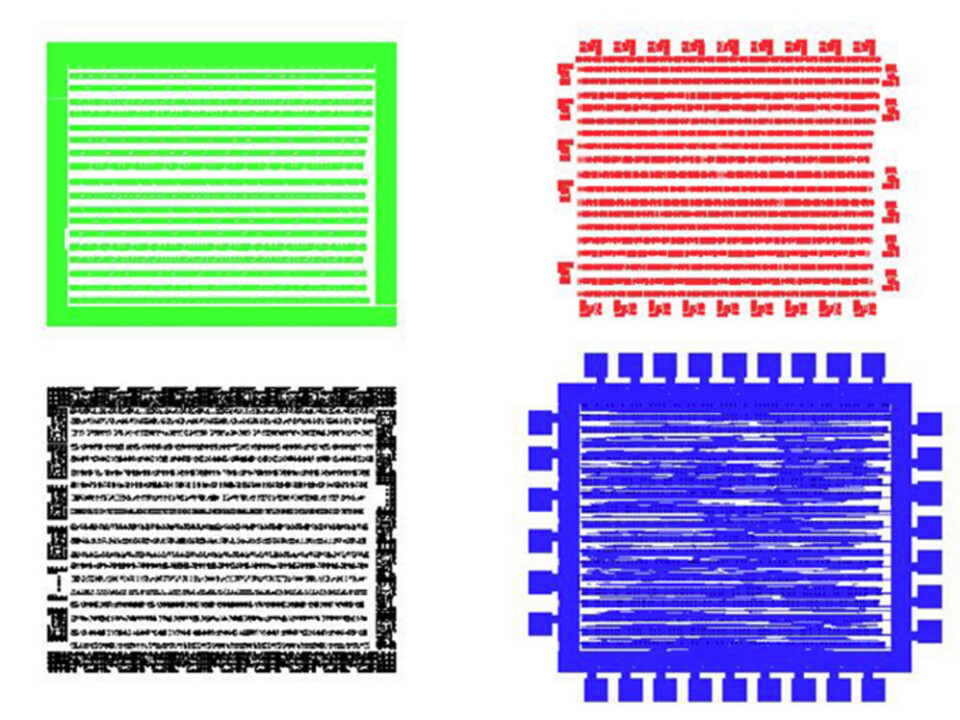

En variasjon over dette tema som tilbys av X-Fab, kan ytterligere redusere kostnaden for produksjon av maskesett. Det skjer ved å tegne flere prosesslag på den samme masken. Figur 3 viser 4 lag som er tegnet på én maske, noe som kutter maskekostnadene med så mye som 70%. Dette er kjent som Multi-Layer Mask eller MLM.

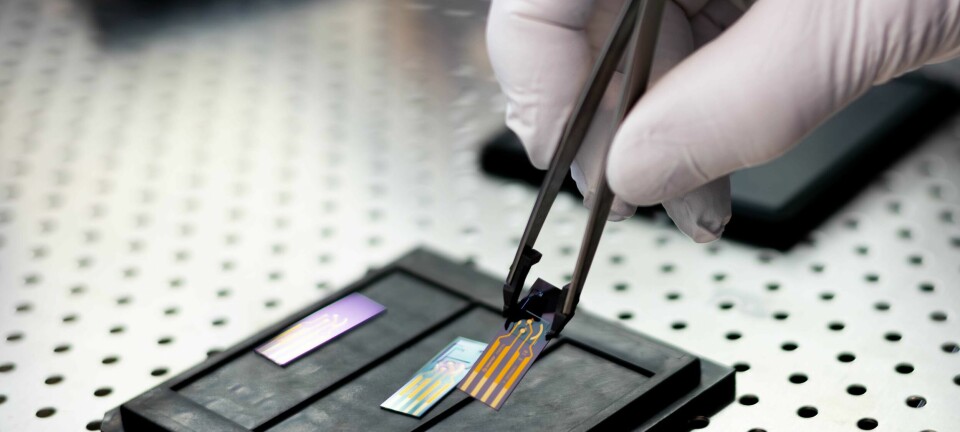

Det er viktig å huske at hverke eldre prosesser eller MPW tjenester er til hinder for ledende analog design. Den første énbrikke Bluetooth.transceiveren, vist i Figur 4, ble utviklet på slutten av 90-tallet av et oppstartsfirma som brukte en 0,35um CMOS prosess. Ganske nylig, da et annet oppstartsfirma utviklet en ny generasjon kommunikasjons-ASIC for å kunne utnytte det nå åpne, ulisensierte spektrumet som tidligere ble benyttet til analog TV-overføring, brukte de verken 14nm eller 40nm, men den nå modne 90nm prosessnoden. Den relativt rimelige skivekostnaden, sammen med utmerket yield, sikret at komponenten kunne tilby tilstrekkelig lav pris i kommersielt prisfølsomme høyvolumapplikasjoner, i tillegg til at man fikk god analog ytelse og modne prosesser som kunne sikre et design som ble ”riktig første gang”.

God tilgjengelighet av rimelig komponentsammenstilling og testtjenester kompletterer hele leveringskjeden fra produksjon, og sikrer dermed at fullt fungerende innkapslede, testede brikker kan leveres enkelt og billig.

Rimelige designverktøy

Bruken av modne prosesser trekker også ned verktøykostnadene. Det er unødvendig å kjøpe kostbare, ledende designverktøy som er tiltenkt avanserte nanometer SoC-design, ettersom de har mange egenskaper som i praksis er unødvendige for design i de modne nodene. For eksempel trenger du et langt mer komplekst og dermed kostbart designverktøy for å kunne utføre simulering, utlegg eller verifikasjon av et design med milliarder av porter i en nylig lansert prosessnode, enn du trenger for en relativt enkel mikset-signalkrets i en moden prosess der portantallet kan være på noen titalls tusen, og det meste av de analoge kretsene er IP-blokker som tilbys av fabrikken og som er brukt mange ganger før.

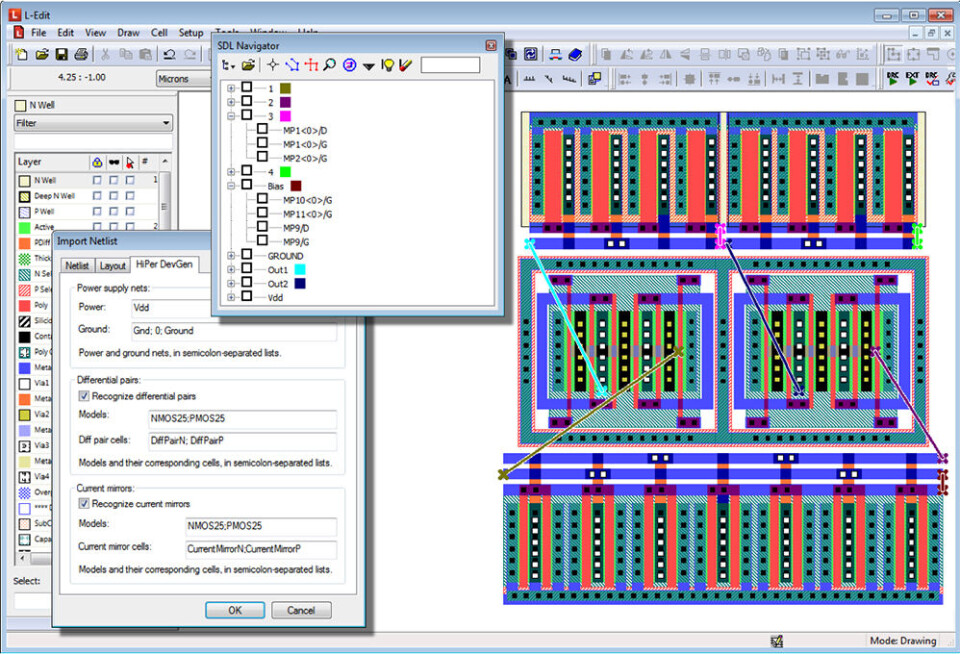

Rimelige designverktøy, slik som Mentor Graphics - Tanner AMS IC Design Flow, som ble brukt i omfattende grad i de ovenfornevnte eksemplene, har støtte for HDL digital design, syntese og plassering og ruting, sammen med støtte for fullt kundespesifisert analogdesign, noe som gjør det mulig for designeren å bevege seg inn i mikset-signal brikkedesign i modne prosesser, enkelt og kosteffektivt.

Når det gjelder den analoge delen av designen, gir de billige og til og med de gratis, åpne verktøyene mange av fordelene som mer avanserte verktøy tilbyr, uten unødvendige funksjoner og kostnader. Rimelige verktøy er ofte enklere å bruke, ettersom de ikke legger avanserte egenskaper i veien for bruken. Dette betyr imidlertid ikke at de mangler funksjonaliteten eller kapasiteten mer avanserte verktøy har, for analog- og mikset-signal design. Figur 5 viser det automatiserte utlegget for en operasjonsforsterker, ved bruk av Tanner EDAs designverktøy.

En annen viktig faktor i valg av designverktøy er lett tilgang til PDKer som trengs for nøyaktig og effektivt design. Dette er gjort enklere gjennom bred aksept i industrien for den voksende standarden Interoperable PDK, eller iPDK. iPDK utvikles av de fleste silisiumsmier i dag, og er utformet for å kunne fungere med alle de vanlige IC-designverktøy. Disse iPDKene inneholder ikke bare grunnleggende prosessrelaterte data som simuleringsmodeller og prosesslag, men også mer komplekse kretsgenereringsmakroer, kjent som parametriserte celler, eller P-Cells. Det pleide å være slik at de fleste verktøyleverandørene brukte proprietære språk for sine P-Cells, slik at silisiumsmiene måtte velge hvilken verktøyleverandør de skulle støtte. Ettersom de fleste verktøyleverandører nå støtter Python som anvendt språk i sine P-Cells, kan fabrikkene støtte alle de viktigste verktøyleverandørene med én PDK.

Lavkostverktøy har en annen besparelse til sin fordel. Løpende kostnader for støtte og vedlikehold er en stor utgift for high-end verktøy. For å kunne håndtere kompleksiteten knyttet til å sette opp og vedlikeholde slike teknologiledende verktøy, krever ofte designflyten støtte av en dedikert DAK-avdeling, eller bruk av kostbare vedlikeholdsavtaler. Dersom du arbeider med et mindre, mikset-signal designteam, må du spørre deg selv om du virkelig trenger å dra på deg kostnaden knyttet til denne typen DAK-støtte, spesielt når mer kosteffektive verktøy er laget for å fungere rett ut-av-boksen.

Et brukereksempel

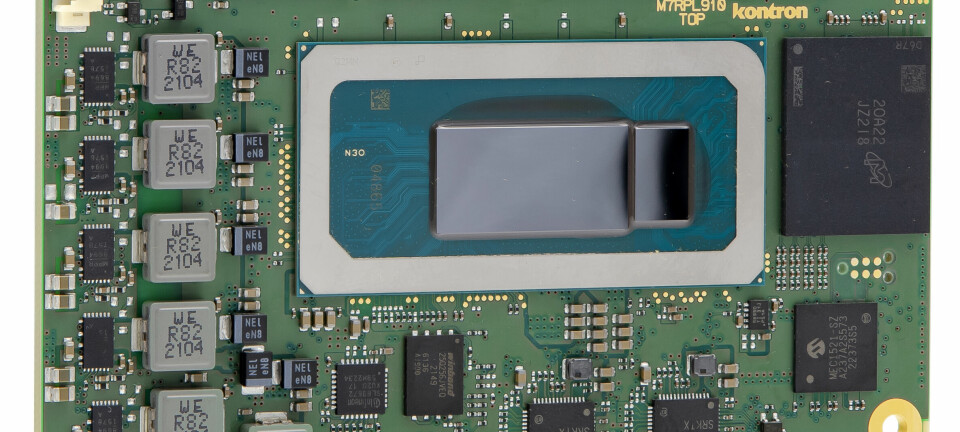

Da det tradisjonsrike, men fortsatt innovative selskapet Rotalink hadde behov for en måte å redusere størrelsen på styringselektronikken i sine elektriske miniatyrmotorer, tok de som vist i Figur 6 i bruk ASIC, ettersom denne løsningen kunne tilby den tekniske kompleksiteten, den analoge funksjonaliteten og den miniatyriserte størrelsen som anvendelsen krevde. Brikken er designet med verktøy fra Tanner, og anvender velprøvde og testede IP-blokker, levert av produksjonspartneren X-Fab. Deres kosteffektive prosess gjør Rotalink i stand til å møte volum- og kostnadsmålene som forventes i det kommersielt aggressive markedet for industrielle styringer. Adm. direktør Melvyn Hazell i Rotalink uttalte “For å kunne holde seg i fronten i et så konkurranseutsatt marked kreves det målrettet satsing på kontinuerlig teknologisk og kommersiell utvikling, og bruk av ASIC hjelper oss å oppnå begge deler.”

Om du tror du vet hva ASIC er, må du tro om igjen!

For modne prosesser er IC-design i ferd med å bli mer tilgjengelig, takket være et stort tilbud av produksjonskapasitet og lavere engangskostnader, noe som er gjort mulig gjennom billige verktøy og rimeligere prosesser. Det er ingen grunn til å tenke at dine eneste muligheter er FPGA eller diskrete mikroprosessorer med analoge tilleggskomponenter på kortnivå. Modne prosesser gjør deg i stand til å spare penger og forbedre ytelsen, ved å legge de viktigste differensierende elementene ved ditt produktdesign i én IC. Kundespesifiserte kretser er ikke lenger forbeholdt selskaper med tykke lommebøker!