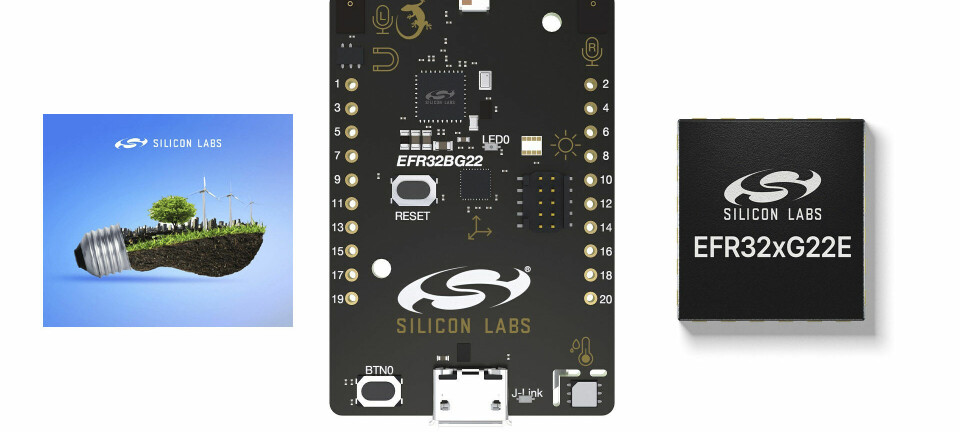

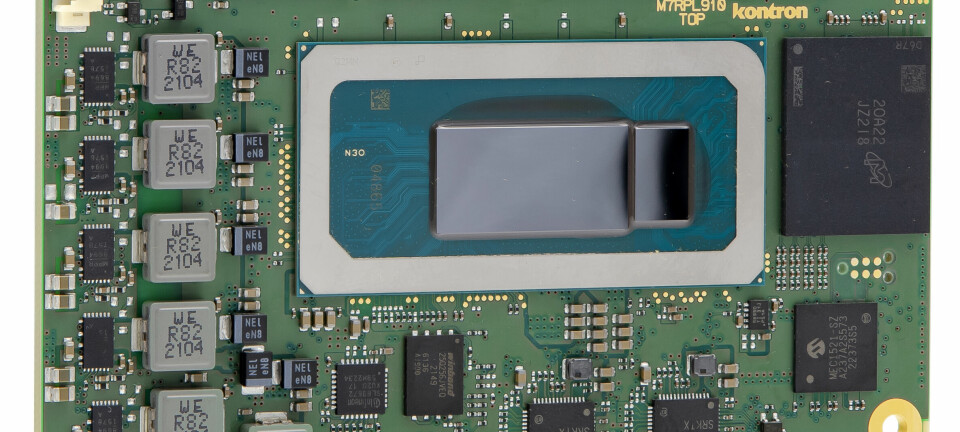

Microsemi med gratis CPU-kjerne i FPGA

Prosessorprosjektet Risc-V, med støtte fra selskaper som Google, HP og Oracle, får nå et tilskudd fra Microsemi. Selskapet lanserer en «mykversjon» i sine FPGAer.

Denne artikkelen er 2 år eller eldre

Dermed er Microsemi den første FPGA-leverandøren som tilbyr Risc-V. Prosessoren skal være kraftigere enn andre myke prosessorer man finner i en FPGA. Dessuten er den sikrere i den forstand at det går an å inspisere den åpne RTL-koden for å sjekke at ingen har manipulert den.

Bakgrunnen for Risc-V er at man kunne starte med et blankt ark og ta fram et 32-bit instruksjonssett for en RISC-prosessor. Dette har foregått en stund i forskningsverdenen, men har i senere tid blitt mer kommersiell, dog fortsatt med åpen kode.

– Det er den store fordelen. Dersom en kunde starter med en FPGA, er det enkelt å gå videre med en ASIC. Man behøver heller ikke forhandle om lisensvilkår for prosessoren, sier Ted Marena fra Microsemi.

Selskapets versjon er døpt RV32I og kan kjøres i FPGA-familiene Igloo2, Smartfusion2 og RTG4. I tillegg til IP-blokk er et Eclipsebasert utviklingsmiljø tilgjengelig, under det egne verktøyet Libero.