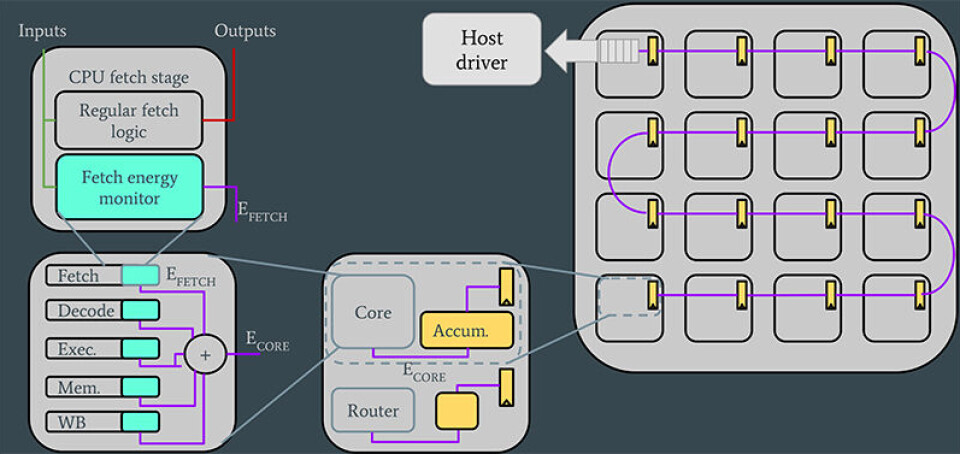

Energieffektivitet med SHMAC

FPGA-er er et vanlig brukt verktøy for validering av ASIC-design, samt vurdering av designets ytelse. Går det an å også bruke FPGA-en til å raskt evaluere designets energieffektivitet?

Denne artikkelen er 2 år eller eldre

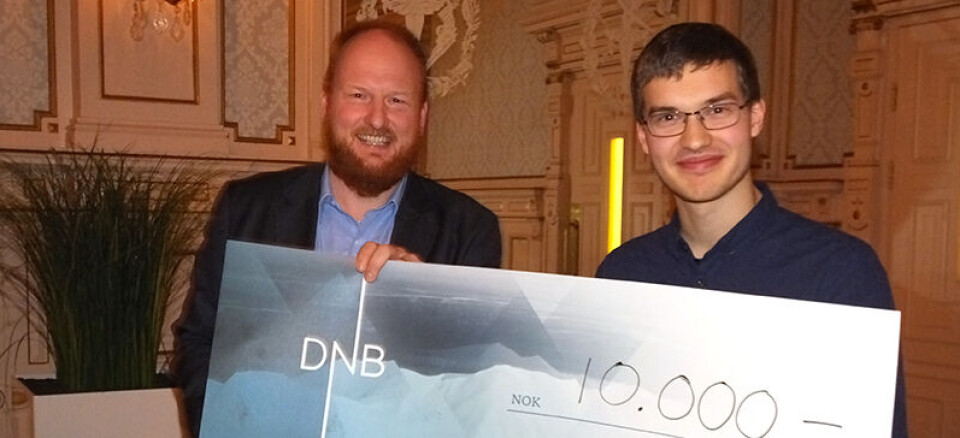

Min masteroppgave ble gjennomført som del av SHMAC-prosjektet [9], et samarbeidsprosjekt mellom institutt for datateknikk (IDI) og elektronikk og telekommunikasjon (IET) ved NTNU. SMAC-prosjektet igjen er en del av IME-fakultetets forskningsfyrtårn EECS [8]. I prosjektet ønsker vi å kartlegge avveininger i forhold til konstruksjon og utnyttelse av heterogene flerkjernearkitekturer, med spesielt fokus på energieffektivitet. For å få til dette, er det laget en infrastruktur som skal gjøre det enkelt å eksperimentere med forskjellige varianter av heterogene arkitekturer. Denne infrastrukturen kalles SHMAC-infrastrukturen, og planlagt bruksmåte er illustrert i figur 1. Forskere kan konstruere forskjellige typer prosessorkjerner, og infrastrukturen definerer hvordan disse kobles sammen. Forskjellige kombinasjoner av heterogene kjerner kan så konstrueres ved å koble et utvalg av de eksisterende kjernene sammen etter ønske.

Behovet for estimering av energiforbruk

For å få evalueringen av forskjellige SHMAC-instanser til å gå fort, implementeres designene på en FPGA. Dette gir mulighet til å evaluere hvor raskt designet opererer i form av antall klokkesykler brukt til å utføre et visst program. Designets energieffektivitet er imidlertid ikke en egenskap man uten videre kan utlede fra FPGA-emuleringen. Merk at FPGA-systemet for SHMAC-prosjektets formål er å anse for en simulator, og en måling av dette systemets energiforbruk vil ikke gi oss svar på hvor mye energi en ASIC-variant av SHMAC-instansen ville brukt. Da energieffektivitet står i høysetet i SHMAC-prosjektet, er en måte å oppdrive energiforbruksestimat på svært viktig. Målet med min masteroppgave som jeg diskuterer i denne artikkelen var derfor å utrede muligheten for å få slike estimat fra SHMAC-infrastrukturen, og om mulig implementere dette.

Vanlige metoder uegnet

Under design av ASIC-system, brukes vanligvis spesialprogramvare for å analysere effektforbruket til ens krets under en viss last. Dette kan gi nøyaktige estimat, men kjøretiden til disse verktøyene er svært lang. Som et eksempel, tok det 60 timer å beregne effektforbruket fra to millisekund programaktivitet på en SHMAC-konfigurasjon. Verktøyene kan følgelig ikke brukes direkte til å komplementere SHMAC-infrastrukturen, da de ikke kan holde tritt med en FPGA-emulering.

Teknikk som fungerer?

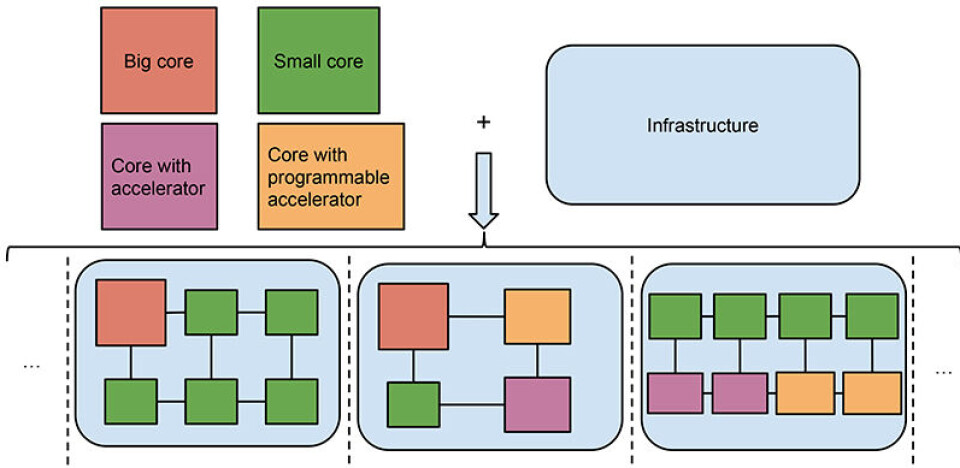

Behovet for et raskere alternativ til spesialprogrammene har blitt behandlet i forskning tidligere. Et vanlig alternativ er konstruksjon av en regresjonsmodell som relaterer signalaktivitet til effektforbruk [5]. Spesialprogrammene er fortsatt nødvendige, men brukes kun én gang til å regne ut treningsdataene man bruker til regresjonen. Regresjonsmodellen kan så brukes til å raskere regne ut estimat, dog med lavere nøyaktighet.

For å bruke denne typen modeller i SHMAC-infrastrukturen, er det også nødvendig med en måte å knytte utregning av modellenes prediksjoner til aktiviteten samlet fra FPGA-systemet. Et alternativ er en teknikk kjent som power emulation [6]. Teknikken forutsetter at regresjonsmodellen er konstruert med enkle ledd, som lineære kombinasjoner av signalverdier. Deretter utnytter man innsikten om at slike enkle uttrykk kan implementeres i hardware.

Utregning av estimatene kan slik gjøres i sanntid ved å koble signaler i systemet man emulerer til en hardware-implementasjon av modellen. Kombinasjonen av regresjonsmodellering og power emulation er illustrert i figur 2.

Fra teori til praksis

Disse teknikkene gav oss en teoretisk mulighet til å utvide SHMACinfrastrukturen med et rammeverk for estimering av energiforbruk. Neste ledd av arbeidet var å omsette potensialet i praksis. Dette var et todelt arbeid: design av et hardware-rammeverk som utvider SHMAC-infrastrukturen med energiestimering og raportering av estimatene, og utvikling av modeller for komponenter i SHMAC. Dette tar vi for oss i det videre.

Integrere modeller

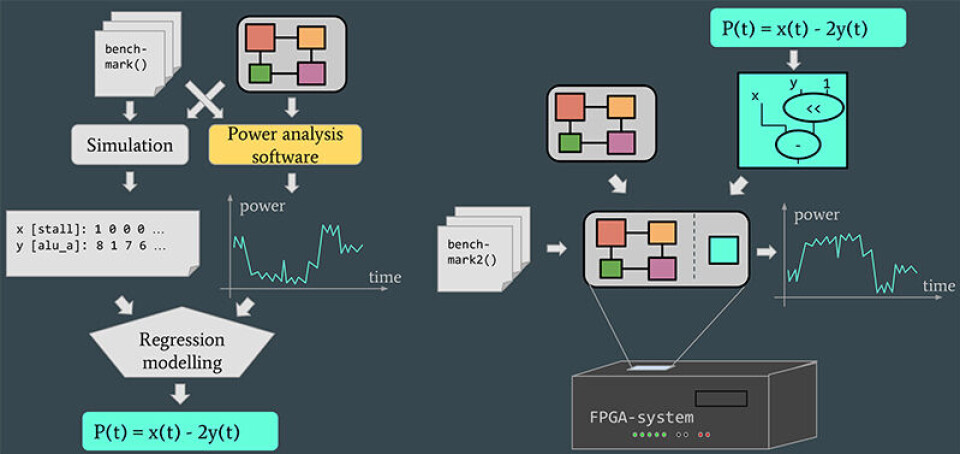

Den overordnede implementasjonen av rammeverket er avbildet i figur 3. Figuren viser fire hierarkiske rammeverksnivå. De to første illustrerer hvordan hardware-implementasjoner av modeller integreres i SHMAC-infrastrukturen, mens de to siste viser hvordan estimatene rapporteres. Som forklart, regner modellen av energiforbruket til en gitt modul ut sitt estimat basert på signalaktivitet i modulen. Det er dermed enkelt å integrere disse modellene i rammeverket: man utvider modellerte moduler med hardware-implementasjonen av modellen, og ruter inputsignalene til 3.

Hierarkisk

Rammeverket støtter hierarkiske modeller, hvor energiestimatene for en foreldrenode består av summen av estimat fra barnenoder. Denne typen modeller kan enkelt integreres ved å summere bidrag modeller integrert i barnemodulene, som illustrert nederst til venstre i figur 3.

Rapportere estimat

Estimat regnes ut hver klokkesykel, men å rapportere data like raskt er upraktisk. I stedet baserte jeg meg på periodisk avlesning av akkumulerte data. Denne støtten er illustrert i midten av figur 3. Energiestimatene rutes til en akkumuleringsmodul, som styrer inputverdien til et måleregister.

SHMAC-infrastrukturen er koblet til et vertssystem, som har mulighet til å drive et målesignal. Når målesignalet aktiveres, lagres de akkumulerte dataene i måleregisteret og akkumuleringsmodulen nullstiller sin tellerverdi. For å frakte data ut til vertssystemet, er måleregistrene koblet sammen som et skiftregister. Etter at en måling er gjennomført, vil måleregistrenes verdier overføres én etter én inn i en kø. Denne køen kan så avleses fra vertssystemet. Dette maskineriet er avbildet lengst til høyre i figur 3.

Regresjonsmodellering

Lineær regresjon forsøker å finne koeffisienter _i til ledd xi(t) for best å tilnærme en responsvariabel y(t): y(t) = P ixi(t). Selve modelleringsjobben vil derfor i all hovedsak handle om å velge ledd xi som fører til god modellnøyaktighet men som ikke er for kostbare å implementere i hardware. For SHMAC-infrastrukturen gikk jeg manuelt til verks. Som valg av xi brukte jeg i stor grad kontroll-signal som styrer multipleksere, og Hamming distanseutregning for viktige buss-signal. Det har også blitt gjort forsøk i forskningsarbeid på å automatisere denne formelkonstruksjonen; eksisterende alternativ diskuterer vi i et oppfølgingsarbeid [4].

I tillegg til selve modelleringen, er det nødvendig at man:

1. Syntetiserer designet som skal modelleres.

2. Velger ut program til å generere trening- og testdata til modellering.

3. Kjører programmene gjennom simulator og effektanalyseverktøy for å generere data.

4. Konverterer data til modelleringsvennlig format.

5. Gjennomfører den faktiske modelleringen.

6. Implementerer modellene som hardware-moduler.

Mye innsats

Dette er følgelig et punkt som krever mye innsats med oppsett av verktøy. I arbeidet med oppgaven fikk jeg god hjelp fra ansatte ved IET til å sette opp den nødvendige ASIC-verktøykjeden. Spesielt interesserte kan finne fullstendig redegjørelse for detaljene rundt disse punktene i masteroppgaven [2]. Nytteverktøy samt støttebibliotek for modellering er gjort tilgjengelig som et supplement til overnevnte oppfølgingsarbeid [1].

Analytisk modellering

Ikke alle komponenter egner seg til regresjonsmodellering. Dette gjelder især on-chip og off-chip RAM-ressurser. On-chip RAM-ressurser er ikke implementert med spesialtilpassede SRAMmoduler i SHMAC-infrastrukturen, og effektestimatene man får vil derfor ikke representere en realistisk prosessorfabrikasjon. I stedet brukte jeg CACTI-verktøyet [10] til å estimere forbruket til en representativ SRAMblokk.

Ekstern RAM

Off-chip RAM kan vi heller ikke lage regresjonsmodeller for, da aktiviteten er utenfor SHMAC-systemet. Her trenger vi imidlertid heller ingen nøyaktig modell, siden SHMAC-prosjektet ikke fokuserer på minnekonstruksjon. Jeg lagde derfor en enkel modell basert på estimat for energiforbruk per lese- og skriveaksess utledet fra et regneark fra Micron [7].

Fungerer det?

I evalueringen av teknikken, er det særlig to aspekt som er aktuelle:

1. Hvor nøyaktige klarer vi få modellene?

2. Hvor mye hardware-ressurser koster det å implementere rammeverket, inkludert modeller?

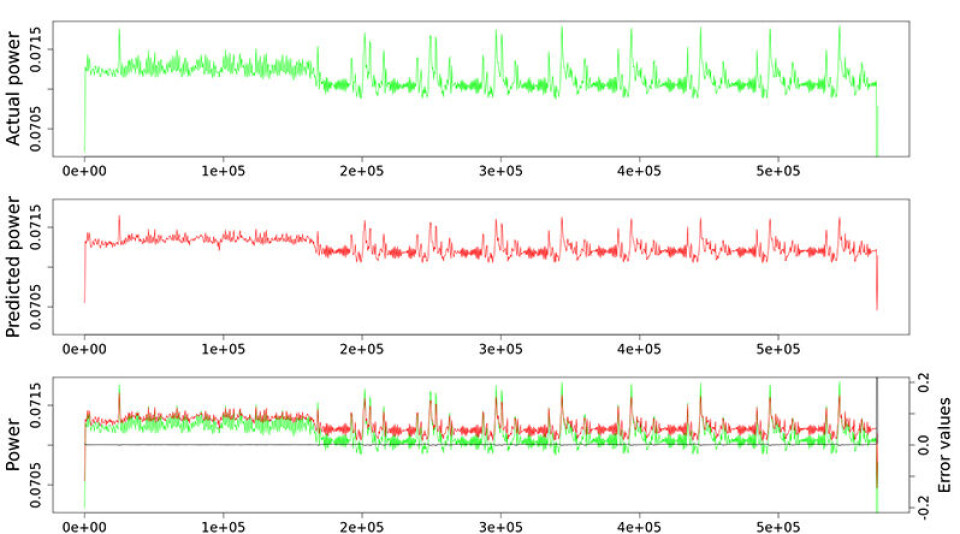

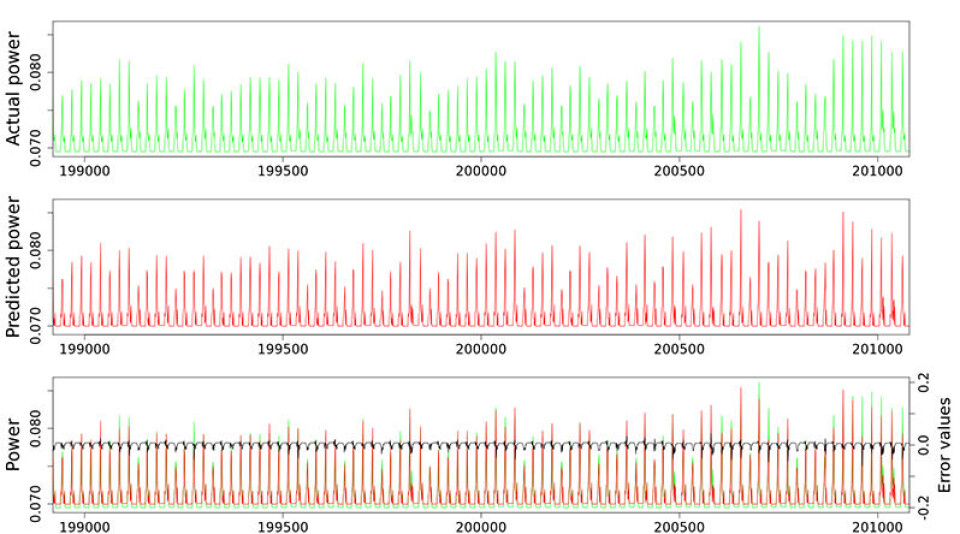

I modellkonstruksjonen fokuserte jeg på å få så høy nøyaktighet som mulig, for å vurdere potensialet til modelleringen. Reduksjon av hardwarekostnad var ikke et fokus. Denne prioriteringen gjenspeiles også i resultatene. For å måle nøyaktighet, brukte jeg først ASIC-analyseverktøy til å regne ut energiforbruket til en annen applikasjon enn den jeg brukte til å lage modellen. Deretter brukte jeg modellen til å beregne energiforbruk for den samme applikasjonen. Sammenlikningen mellom estimatene er illustrert i figur 4. Figuren plotter gjennomsnittet av måleverdier fra 500 sykler av gangen. Feilen i estimatet for totalt energiforbruk for applikasjonen er på 0.19 %. Et utsnitt av estimat for enkeltsykler er gjengitt i figur 5. Den gjennomsnittlige feilen for estimat i hver sykel er på 1.1 %.

Overhead i beregningen

Denne nøyaktigheten kommer imidlertid ikke gratis. For å implementere disse modellene, kreves det totalt 8037 LUTs og 4032 flip-flops. Dette tilsvarer en overhead på nesten 55 %. Majoriteten av denne kostnaden stammer fra Hamming-distanseutregning, især for ruter-modulen hvor modellen består av summen av Hamming-distansen til 15 busser på 196 bit hver. Ser vi kun på prosessorkjernen, er overheaden tilnærmet 18 %.

Selv om totaloverheaden nok kunne vært redusert med mer målrettet modell-optimalisering og med en mer konvensjonell ruter-implementasjon, er SHMAC-kjernen som er modellert et forholdsvis enkelt design. Hvis man ønsker høy sykelvis nøyaktighet i estimatene, bør man belage seg på å avse en god del FPGA-ressurser. Hvis man bare ønsker å estimere gjennomsnittsenergiforbruk, kan man slippe unna med langt billigere modeller. I vårt oppfølgingsarbeid så vi for eksempel at man med bare 76 LUTs kunne lage en modell med en feil på 6 % i estimert totalenergiforbruk.

Konklusjon

Vi har sett hvordan den FPGA-baserte SHMAC-infrastrukturen ble utvidet med støtte for estimering av energiforbruket til designet som er implementert på FPGAen. Nøyaktigheten til estimatene er høy, men dette tar sin pris i hardware-ressurser. Dersom designet man modellerer er tilstrekkelig enkelt, mens FPGA er tilstrekkelig stor, eller man hovedsakelig er interessert i gjennomsnittsenergiforbruk, kan overheaden være akseptabel. Å bruke FPGAsystem til å hurtig evaluere energiforbruket kan derfor være en reell mulighet.

Hvis man ønsker å bruke teknikkene presentert i denne artikkelen, må man også ha ASIC-verktøy tilgjengelig og være villig til å investere tid i utvikling av testprogram og modeller. Hjelpeverktøy jeg utviklet i forbindelse med dette arbeidet er fritt tilgjenglig [1], og kan være nyttig for dette. Mer informasjon om arbeidet er tilgjenglig i min masteroppgave [2] og presentasjonen av denne gitt på FPGA-forum [3].

Referanser

[1] Benjamin A. Bjørnseth. Repository for software framework and data material. https://bitbucket.org/benjambj/energy-model-synthesis.

[2] Benjamin Andreassen Bjørnseth. Enabling Research on Energy-Efficient System Software Using the SHMAC Infrastructure. Master thesis, 2015. http://brage.bibsys.no/xmlui/handle/11250/2352289.

[3] Benjamin Andreassen Bjørnseth. Presentasjon av masteroppgaven, holdt på fpga-forum. http://https://www.dropbox.com/s/xfrilptkuqe1o07/BAB-master-fpga-forum.pdf?dl=0, Feb 2016.

[4] Benjamin Andreassen Bjørnseth, Asbjørn Djupdal, and Lasse Natvig. A Systematic Approach to Automated Construction of Power Emulation Models. In Design, Automation & Test in Europe Conference & Exhibition, DATE’16 (to appear), 2016.

[5] Alessandro Bogliolo, Luca Benini, and Giovanni De Micheli. Regressionbased RTL power modeling. ACM Transactions on Design Automation of Electronic Systems, 5(3):337–372, 2000.

[6] J. Coburn, S. Ravi, and A. Raghunathan. Power emulation: a new paradigm for power estimation. In Proceedings. 42nd Design Automation Conference, 2005., pages 700–705, 2005.

[7] Micron ddr3 sdram data sheet. http://www.micron.com/~/media/documents/products/data-sheet/dram/ddr3/4gb_ddr3_sdram.pdf, Dec 2014.

[8] The EECS research initiative. http://www.ntnu.edu/ime/eecs.

[9] The SHMAC Project. http://www.ntnu.edu/ime/eecs/shmac.

[10] S. J E Wilton and Norman P. Jouppi. CACTI: An enhanced cache access and cycle time model. IEEE Journal of Solid-State Circuits, 31(5):677–687, 1996.