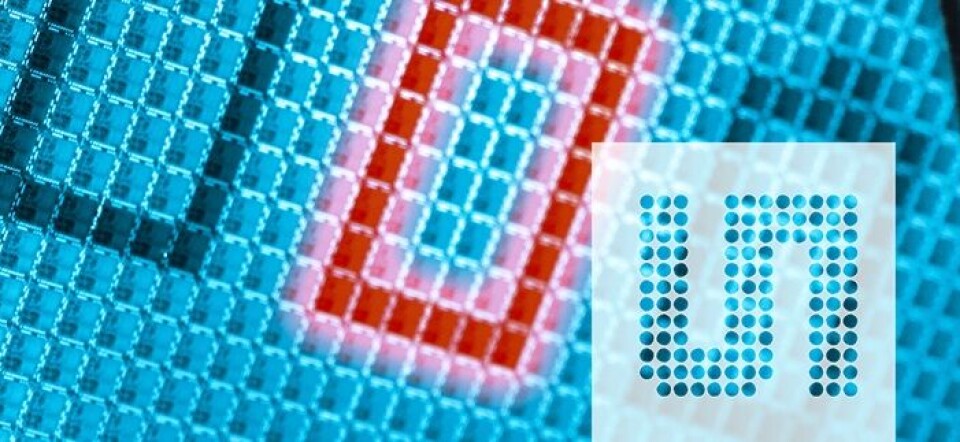

Skalerbare transistorer sparer plass

Østerrikske ams tilbyr nå spenningsskalerbare HV-transistorer i CMOS som skal gi flere transistorer per silisiumskive.

Denne artikkelen er 2 år eller eldre

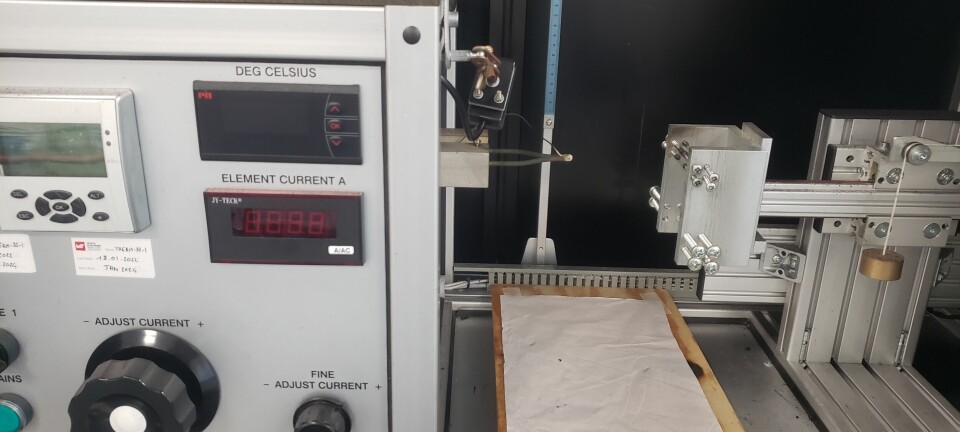

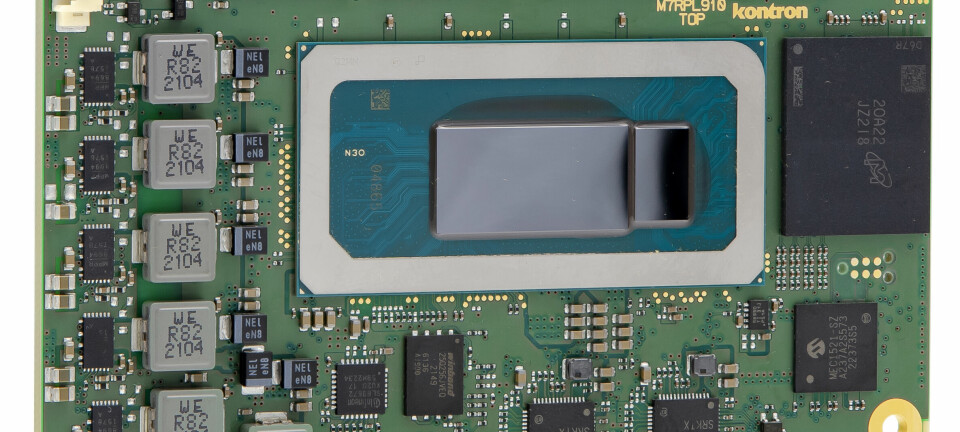

Silisiumsmien til den østerrikske halvlederprodusenten ams, melder at de har utvidet og forbedret sin spesialiserte 0.35µm High-Voltage (HV) CMOS prosessplattform.

Den avanserte “H35” prosessen inkluderer nå et helt sett av skalerbare transistorer, med betydelig areal- og ytelsesforbedringer.

De nye spenningsskalerbare HV NMOS- og PMOS transistorene skal være optimalisert for ulike drain-source voltage nivå (VDS) fra 20V til 100V, og tilbyr betydelig lavere på-motstand og dermed mindre arealforbruk, heter det.

Ved å bruke en optimalisert 30V NMOS transistor i kraftstyringsapplikasjon, i stedet for en fast 50V tansistor, skal det være mulig å spare plass tilsvarende 50% av arealet, hevder ams.

En 60V optimimalisert NMOS komponent skal resultere i 22% mindre område sammenlignet med en standard 120V NMOS transistor.

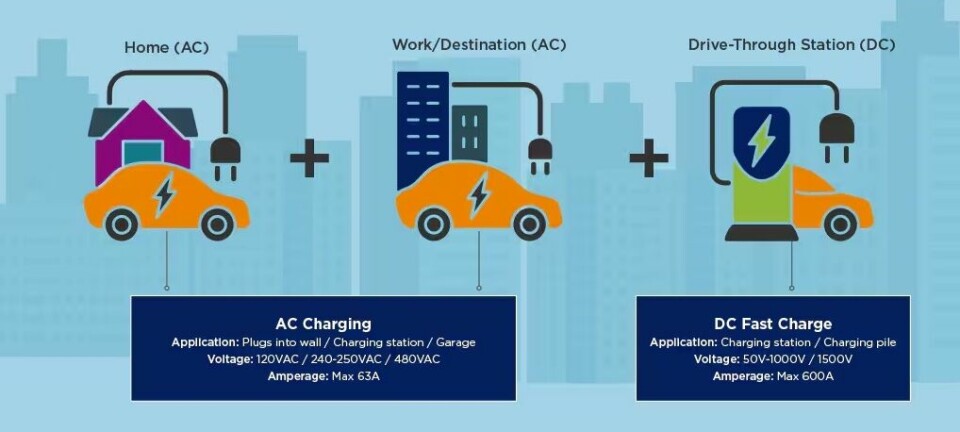

Disse optimaliserte komponentene skal være egnet i et bredt spekter av applikasjoner, som MEMS-drivere, motordrivere, svitsjer og kraftstyringskretser brukt innen bil, medisin og industri.