Et verktøy som kan brukes i designflyten av et PCIe endepunkt

Sensorteknologi er på fremmarsj. Økt bruk av følere i hverdagslig forbrukerelektronikk fører til en akselererende trend i mengden med sensor-data som til en hver tid må bearbeides. Informasjonen må håndteres og analyseres, noe som kan være en stor påkjenning for datasentre. Den stigende etterspørselen av informasjonsbehandling skaper et stort behov for optimalisering av kommunikasjonsinfrastruktur på mikroarkitekturnivå. I mastergradsarbeidet beskrevet i denne artikkelen, er det blitt utviklet en tidsrealistisk transaksjonsnivåmodell av et sentralt knutepunkt i en etablert kommunikasjonsprotokoll, PCI Express.

Denne artikkelen er 2 år eller eldre

I. Introduksjon

Internet of things(IoT) er et mye omtalt scenario i disse dager. Cisco Systems, et amerikansk internettbasert selskap, har estimert at det innen år 2020 vil være over 50 milliarder enheter koblet direkte til Internett[2]. Majoriteten av disse enhetene vil være sensornoder som genererer data i store mengder, sender dette til basestasjoner som så overfører dette videre med IPv6 til datasentre. En utfordring med IoT er “Big Data Analytics”, altså analyse av innsamlet rådata for å se essensen i den underliggende informasjonen. Det krever datasentre med god nok infrastruktur til å tåle de store påkjenningene fra den økte datatrafikken. Effektiv kommunikasjon helt fra sensornoder og opp til skyen, er en viktig nøkkel for at en IoT-forretning skal lykkes.

Oracle Corporation, verdens nest største softwareselskap, utvikler og leverer databaseprogramvare. Det få vet er at de også produserer hardwareløsninger i symbiose med den egenutviklede programvaren. Dermed kan de levere komplette løsninger til datasentre, helt fra hardwarenivå og opp til sky-nivå. Bedrifter som ønsker å tilby skytjenester eller som kun har behov for raske og sikre lagringsløsninger, kan ta nytte av slike enterprise-løsninger.

Masteroppgaven som vant mikroelektronikkprisen, 2014, er skrevet i samarbeid med Oracles avdeling på Skullerud, i Oslo. Som del av Oracles globale utviklingsteam innen enterprise-systemer, bidrar de med utvikling av kommunikasjonsinfrastruktur i enterprise-produktene. På hardwarenivå i løsningene som tilbys av Oracle, inngår det blant annet integrerte kretser (ASICs) med ”Peripheral Component Interconnect Express”(PCIe) og ”Infiniband” teknologi. Ved å inkludere slike kommunikasjonsprotokoller i datahåndterings-ASICs, får man muligheten til å flytte data hurtig mellom prosesseringsenhetene internt i maskinene i datasentre. Optimalisering av infrastruktur på et så lavt abstraksjons-nivå, gir høy nok ytelse til at virtualisering av databaser i et datasenter blir en attraktiv mulighet. Virtualisering innebærer at selv om data ligger lagret på forskjellige fysiske lokasjoner, skal informasjonen være tilgjengelig som om den kun ligger i en database. Integrerte databaseløsninger som virtualisering gjør det lettere å administrere IT-løsninger for IT-servicepersonell.

II. PCIe

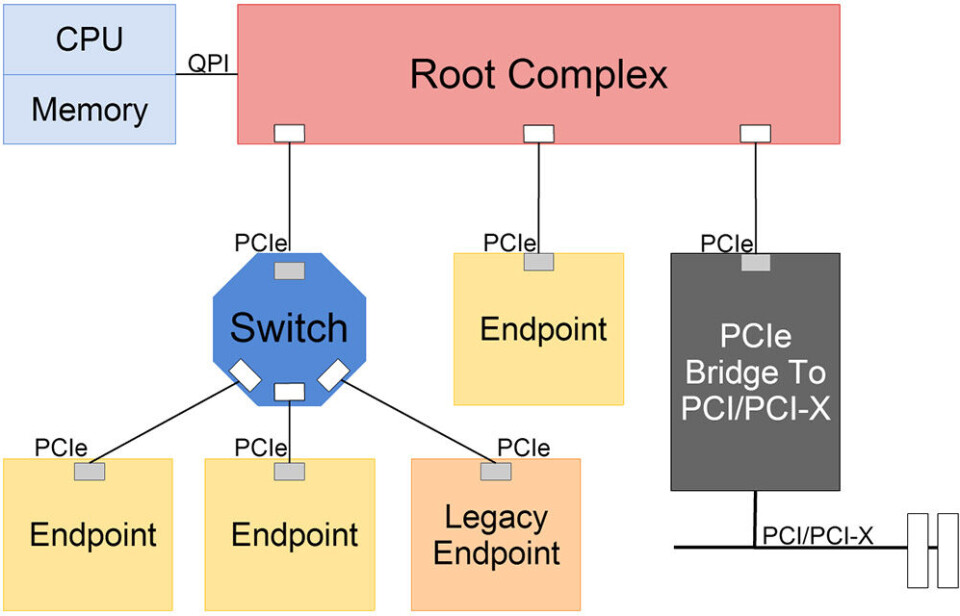

PCIe er en seriell, pakkebasert, kommunikasjonsstandard som er mye brukt i mange av dagens datamaskinarkitekturer for dens gode ytelse. Figur 1 viser et moderne hovedkort fra MSI med tredje generasjons PCIe kontakter for tilkobling av grafikkakseleratorer. PCIe er kommunikasjonsnettverk bygd på et switch-basert hierarki av periferienheter. Nettverket har en typisk trestruktur lik den som er vist i figur 2. Ruting av datapakker blir foretatt mellom enheter som er knyttet til forskjellige grener i PCIe treet. Roten i et PCIe-tre, også kalt rotkomplekset, er treets kommunikasjonskanal for henvendelser til minnet og prosesseringsenheten i maskinen.

Alle datahenvendelser imellom nodene i treet er nødt til å følge PCIe protokollen. Den er lagdelt og består av et fysisk lag, et datalinklag og et transaksjonslag. I tillegg har enheter et programvarelag hvor overordnet funksjonalitet for enhetene er definert. I de forskjellige lagene er det logikk og buffere av varierende størrelser for sending og mottagelse av pakker. Den lagdelte protokollstrukturen sørger for at informasjonen kommer frem slik den skal, dit den skal og til riktig tid. Kommunikasjon i et PCIe system består av flere pakketyper, pakketypen av interesse for transaksjonsmodellering er navngitt; ”Transaction Layer Packet”(TLP). En TLP består i hovedsak av et informasjonshode, en datalast og en hale med verifiseringsinformasjon for å markere slutten av pakken. Informasjonen i hodet forteller blant annet; hva slags TLP det er, hvor denne skal og hvor mye datalast som følger. Pakken blir opprettet i transaksjonslaget og sendt nedover i abstraksjonslagene hvor den blir innkapslet i flere skall for deretter å bli sendt. Pakken blir rutet frem dit den skal ved at switcher sammenligner mottaker-adressen i pakkens TLP-hode med informasjonen i konfigurerte adressetabeller og portlister for nettverket. Når pakken ankommer sin rettmessige eier, blir lagene skrelt av på vei oppover mot transaksjonslaget og datalasten som ligger sentralt i løkstrukturen blir hentet ut av pakken.

I et PCIe nettverk, holder de tilkoblede enhetene på unik eller kopiert data i lokalt minne. Informasjonen kan enten skjules eller være tilgjengelig for de andre aktørene i nettverket. Dersom den er tilgjengelig for andre, sies informasjonen å ligge i systemminnet, og har derfor en dedikert system-minneadresse. PCIe endepunkter har mulighet til å etterspørre data fra systemminnet, både det som ligger lokalt hos de andre aktørene i nettverket og fra resten av systemminnet som ligger bak rotkomplekset. Dette gjøres ved at enheten som ønsker data fra systemminnet, sender en TLP med en minne-forespørsel oppover i nettverket. Pakken blir tolket av den fullførende aktøren, relevant informasjon blir mellomlagret og pakken blir deretter slettet. Siden det ble mottatt en forespørsel, blir en ny såkalt fullføringspakke opprettet, etterspurt data blir hentet ut fra lokalt minne og pakket inn i TLPen. Pakken med datalast blir deretter sendt tilbake til den etterspørrende PCIe-aktøren gjennom PCIe-nettverket.

III. Ytelse i nettverks-arkitektur

Det er ofte to begreper som blir brukt når ytelse i pakkebaserte nettverk diskuteres, latency og jitter. Når man snakker om latency, også kalt latens eller delay, så er det snakk om hvor lang tid det tar for en forsending. Rundtur-latency kan også defineres. Det er tiden det tar fra en dataetterspørsels-pakke blir sendt, til fullføringspakken med etterspurt data kommer tilbake. Jitter er et begrep for usikkerheten i latency. Dersom, til eksempel rundtur-latencyen hadde vært normalfordelt, så hadde jitter direkte beskrevet standardavviket. Jitter i PCIe bestemmes av hvor lenge pakker blir sittende fast i buffere på vei til sin destinasjon, noe som varier fra sending til sending avhengig av kø-status i systemet. Det er ønskelig å minimere både latency og jitter i et PCIe system.

IV. Problemstilling

For selskap som driver med ASIC design, er det viktig å komme tidlig ut på markedet med solide og konkurransedyktige produkter. Det er derfor essensielt å ta i bruk nøyaktige simuleringsverktøy for å redusere utviklingstiden. Designtiden kan bli kraftig redusert når antallet nødvendige prototype-iterasjoner minker. Simuleringsverktøy kan hurtig være med å optimalisere bufferstørrelser og prioriteringsalgoritmer med tanke på totallsystemets Jitter og Latency.

Oracle formulerte en oppgave i midten av desember, 2013. Der ble det ble definert et behov for en nøyaktig, høynivå, simuleringsmodell for et PCIe rotkompleks. Verktøyet skulle kunne simulere miljøet som et PCIe endepunkt designes for.

V. Implementasjon av rotkomplekset

Modellen ble utviklet i SystemC, et rammeverk til programmeringsspråket C++. SystemC egner seg spesielt godt til høynivå modellering av interaksjon mellom moduler. Rammeverket gjør det mulig å utføre kommunikasjons-simulering i små tidskvantum. En modell i SystemC er derfor godt egnet til simulering av systemer med Jitter og Latency.

Rotkompleksets funksjonaliteter ble implementert ved hjelp av klassedefinisjoner for enkel instansiering i flere av systemets aktører. Rotkomplekset ble satt sammen av en switch-modul, en protokollmodul og en delay-simuleringsmodul. CPU med minne ble også modellert til å snakke direkte med rotkomplekset, både som en spørrende aktør, men også som en fullførende aktør i PCIe nettverket.

Delay og jitter er viktig å optimalisere når man designer et PCIe endepunkt. Derfor er det kritisk at en transaksjonsnivåmodell av et rotkompleks er realistisk med tanke på handlingstid og bufferusikkerhet. Dette ble oppnådd ved å implementere en konfigurerbar liste med forsinkelsestider i Rotkomplekset. Det er dermed opp til endepunkts-designeren å definere forsinkelsene riktig før simulering, ut ifra hvilken forsinkelsesfordeling rotkomplekset har i det aktuelle PCIe-systemet.

Forsinkelsesfordelingen til rotkompleksmodellen kan gjøres tilnærmet identisk den til et ekte, fysisk, rotkompleks. Dette kan oppnås ved å faktisk monitorere pakketrafikken på en PCIe bus. Tiden det tar fra en forespørsel er sendt fra et endepunkt, til den tilhørende fullføringspakken blir returnert fra rotkomplekset, blir målt og kan direkte brukes i modellen. Dette ble demonstrert med et vilkårlig data-etterspørrende PCIe endepunkt, et mellomkoblingskort som tillater tyvlytting og en protokollanalysator fra LeCroy. Pakkesporingen ble foretatt på en aktuell 1. generasjons rotkompleksarkitektur i en SUN FIRE X4170M3 server vist i figur 3.

Et script ble også laget og kjørt sammen med sporingsfilene fra protokollanalysatoren. Sporingsfilene ble konvertert til et format som er lesbart av SystemC-rotkompleksmodellen. Det vil si en enkel liste bestående av ekte forsendelses-forsinkelser, oppgitt i nanosekunder.

Rotkompleksmodellen er laget slik at hver gang rotkomplekset mottar en etterspørselspakke, så klargjøres etterspurt informasjon og en timer startes med nedtellingstid lik en vilkårlig trukket, realistisk, forsendelses-forsinkelse. Pakken kan sendes i retur først når timeren har telt ned til null. Så lenge man har nøyaktig nok timingdata kan alle pakketyper modelleres med nøyaktighet lik den til protokollanalysatoren.

Det ble også opprettet en endepunktsmodul med en PCIe protokollstack for å kunne teste rotkompleksmodellen. Endepunktsmodulen er tilsvarende den Oracle er nødt til å implementere i SystemC for endepunktet som designes. For testformål ble endepunktets funksjonalitet konfigurert til å etterspørre og skrive data fra og til fraksjonen av systemminnet bak rotkomplekset. Data ble skrevet og etterspurt i ulike mengder og med varierende hyppighet.

VI. Verifisering av funksjonalitet og timing

Systemkomponenter ble koblet sammen i et testbenkprogram og flere testscenario ble programmert inn i programvarelaget både i test-endepunktet og i den modellerte CPU-en. Testene verifiserte at prinsippet med simuleringsverktøyet fungerte slik det skulle, med en nøyaktighet gitt av tidskvantumet til protokollanalysatoren. Systemet ble også stress-testet med mange hyppige forespørsler for å fylle opp pakkebuffere i switcher og i endepunkter.

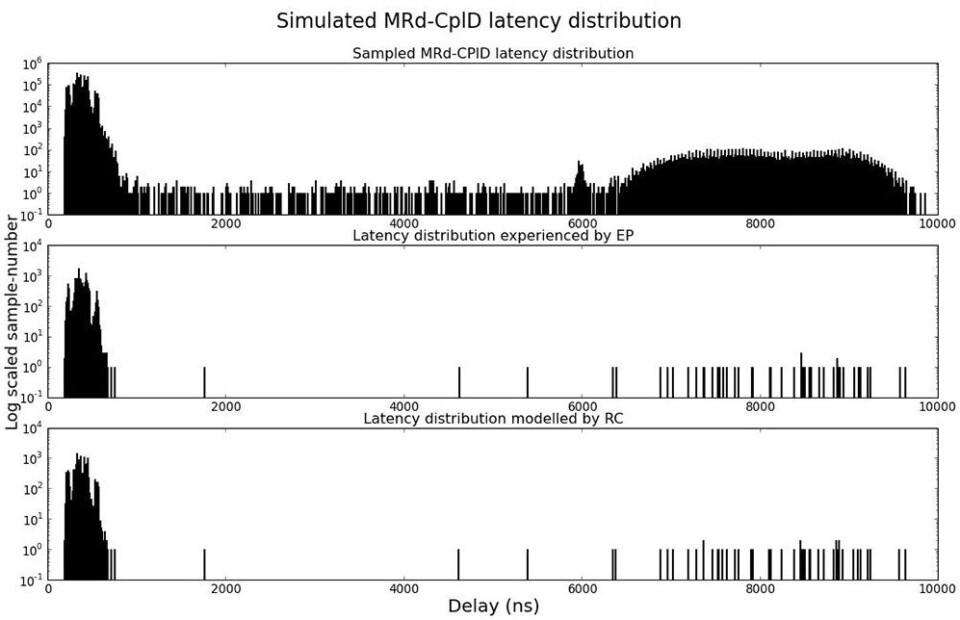

Det simulerte rotkomplekset viste seg å svare på forespørsler med en forsinkelsesfordeling som tilsvarer den som ble lest ut av server-arkitekturen. Figur 4 viser samsvaret mellom ekte forsinkelsesfordeling, fordelingen av forsinkelsene som er simulert og fordelingen av forsinkelsene som er oppfattet av det spørrende endepunktet. Sistnevnte er tilnærmet identisk like forsinkelsene som blir simulert av rotkomplekset, det er kun mulig å se små imperative bufferforsinkelser fra switchene i systemet. Disse kan elimineres ved at switchene fjernes fra PCIe treet om det ikke finnes switcher i endepunktets faktiske omgivelser.

VII. Konklusjon og veien videre

SystemC-modellen viste seg å være en god imitasjon av rotkomplekset i en SUN FIRE X4170M3 server. Det representerte både funksjonalitet og timing på en realistisk måte i et transaksjonsnivå. Pakker ble rutet dit de skulle og modellerte forsinkelser var så og si identisk like de til mål-plattformen. Prinsippet om en slik tidskorrekt modell, vil gi mer nøyaktige bilder av endepunktets ytelse enn anvendte simuleringsverktøy gjør i dag. Dette gir igjen muligheten til å optimalisere endepunktet som designes ytterligere, tidlig i designfasen. Modellen vil, med riktige sporingsdata, korrekt kunne modellere alle generasjoner av PCIe.

I videre arbeid bør verktøyet gjøres mer robust for lange simuleringer og brukervennligheten bør økes. Det er også et behov for å utvikle en fremgangsmetode for nøyaktig SystemC-modellering av endepunktet som designes.

Takk Til

Morten Schanke, Brian Manula, Håkon Bugge og andre ansatte ved Oracle Norway på Skullerud, for et inkluderende og lærerikt opphold. Og til professor Snorre Aunet ved NTNU for god veiledning igjennom utførelsen av masteroppgaven.

Referanser

[1] Bilde av et MSI Z77 hovedkort: http://computerpad.ae/wp-content/uploads/2015/01/msi_z77a_gd55_01.jpg

[2] MacManus, R. "Cisco: 50 Billion Things on the Internet by 2020 [Infographic]." ReadWrite. http://www. readwriteweb.com/archives/cisco_50_billion_things_on_the_internet_ by_2020. php [access 24 Jan 2013] Exploring Asian Ethics for New Technologies 39 (2011).

[3] Anderson, Don, and Tom Shanley. PCI express system architecture. Ed. Ravi Budruk. Addison-Wesley Professional, 2004.

[4] Låte, Even. Masteroppgave: "Transaction Level Modeling of a PCI Express Root Complex." (2014).

[5] Låte, Even. SystemC kildekode av RC-TLM på github: https://github.com/Pufferfish/tlm-of-a-pcierootcomplex-systemc.git, 2014.

Even Låte.

Even Låte.