Hvordan gjøre et “stille” ADC-design for trådløse systemer

I denne artikkelen ser Linear på hvordan man kan oppnå bedre mottakerfølsomhet med en stillegående AD-omformer (ADC) og lavenergi SiGe forsterkerblokker

Denne artikkelen er 2 år eller eldre

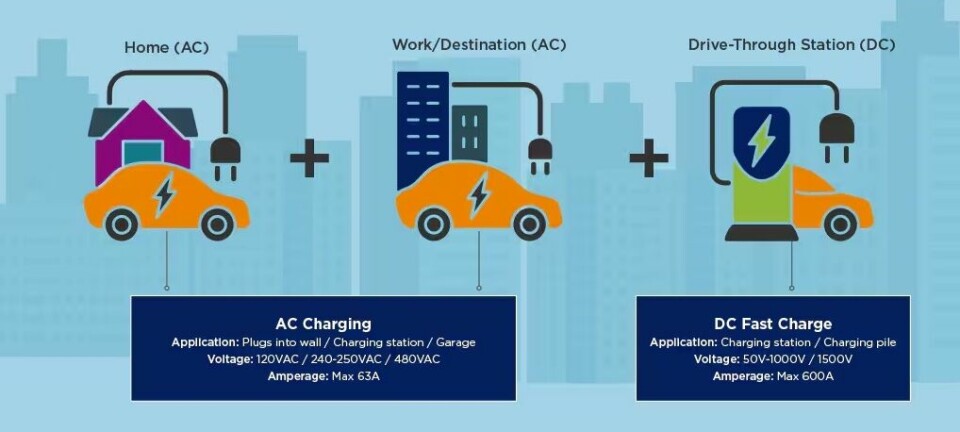

I moderne kommunikasjonssystemer er det gjerne slik, at jo stillere inngangsnettverket er, jo mer følsom er mottakeren. Mottakerseksjonen i systemet er svært sensitivt overfor støy som kommer fra andre kilder. Disse støykildene kan være FPGAen, strømforsyninger eller digitale signaler fra analog-digital-omformeren (ADC). Ved å designe en kompakt løsning, kan barrierer etableres mellom disse støykildene og den analoge inngangen for å redusere støy som kobles til inngangsnettverket, samtidig som følsomheten i systemet forbedres. En kompakt løsning er kanskje ikke mulig med høyeffektforsterkere med 4W effekttap. Med forbedringer i støyytelsen i et system, kreves lavstøysforsterkere med høy linearitet som mater en «stillegående» ADC for å få til ønsket følsomhet. Flere fordeler med ADC-design, som den nye JESD204B-standarden, har hjulpet designere til å takle designutfordringer som tidligere har begrenset mottakerens følsomhet. Disse fordelene, sammen med nye laveffektsforsterkere, har forbedret systemstøyen.

Utfordringer med forsterkerdesign

Tradisjonelt har det i høyfrekvensapplikasjoner blitt benyttet gallium-arsenid (GaAs) eller indium fosfid (InP) forsterkningsblokker for å oppnå høy linearitet og lav støy. Disse forsterkningsblokkene krever spenninger mellom 9-12V som gir 2-4 Watt effekt per mottakerkanal. Kjøling av mottakerkortet blir en utfordring, og ytelsen i systemet reduseres dersom det ikke kontrolleres. I batteridrevne- eller lavspenningsapplikasjoner, kan tradisjonelle forsterkningsblokker bli et problem på grunn av det høye effekttapet.

Enkelte forsterkningsblokker krever også tilpasningskretser ved inn og utgangen som kan endre seg avhengig av valgt frekvensområde. Dette reduserer den totale båndbredden som et enkelt nettverk kan ta i mot, og for å tilpasse inngangsnettverket, øker designtiden.

I tillegg er de fleste av disse forsterkningsblokkene singel endet, med en innebygget ubalanse. Ubalanse i et hvert system vil resultere i like ordens harmoniske som må filtreres for å oppnå god linearitet. I mange situasjoner kan andre ordens termer være nær passbåndkanten der filterdempingen er lav. Siden andre ordens harmoniske ikke er dempet i disse tilfellene, er følsomheten til mottakeren redusert. Ved å bruke en differensiell forsterkningsblokk fra starten av, kan et balansert nettverk designes og andre ordens harmonisk forvrengning har liten betydning.

Forsterkerløsninger

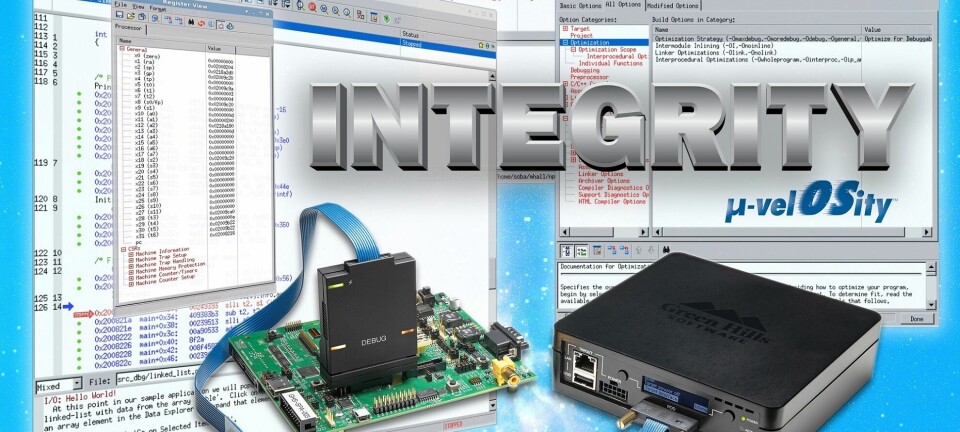

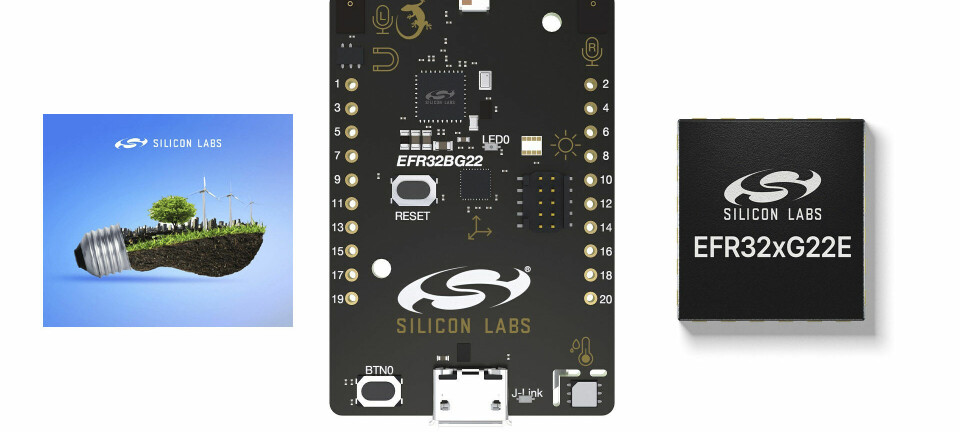

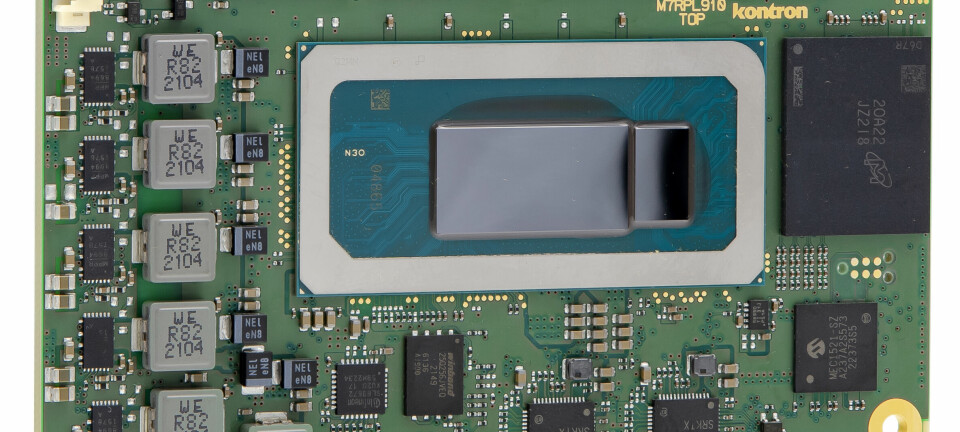

For å kunne redusere energiforbruket i GaAs forsterkningsblokker samtidig som man opprettholder god linearitet og støyytelse, er det nødvendig med en annerledes laveffektprosess. LTC6430 er en differensiell forsterkningsblokk, designet i en lavenergi silisium germanium (SiGe)-prosess som minimaliserer lineariteten og støyytelsen i høyeffekt forsterkningsblokker, med en brøkdel av energiforbruket. Den opererer fra en 5V forsyning og trekker bare 160mA strøm, noe som reduserer effektforbruket til under 1W. Denne effektreduksjonen gjør at LTC6430 kan benyttes i lavenergi, batteridrevne applikasjoner og i temperaturfølsomme applikasjoner, der en tradisjonell forsterkningsblokk ikke ville passet på grunn av den store termiske spredningen.

LTC6430 er stabil med ett samsvarende nettverk, slik at alt som trengs eksternt er DC blokkeringskondensatorer og RF bias choker. Det gjør at forsterkerblokken kan motta frekvenser fra 25MHz til 1600MHz på en enkel krets. Dette reduserer designtiden for inngangsnettverket, slik at mer tid kan brukes på andre kritiske deler av systemet. Enkelheten i dens samsvarte krets reduserer også antall komponenter i tillegg til nettverkskompleksitet mellom ADC og forsterker, slik at det blir mer plass på kretskortet til barrierer og vias som forbedrer hele resultatet til systemet.

Naturlig undertrykking

LTC6430 er en differensiell forsterker som undertrykker like ordens harmoniske naturlig. Den balanserte naturen til LTC6430 produserer kansellering av like ordens harmoniske og forbedrer den totale lineariteten i systemet. Den reduserer også dempingskravene til utgangsfilteret mellom forsterker og ADC. Det enklest mulige balanserte nettverk mellom ADC og forsterker vil gi det beste resultatet ved å gi plass til barrierer og vias for å redusere interaksjon mellom ADC og forsterker. Ved å redusere kravet til filtre, bruker nettverket færre komponenter og vil gi en enkel grensesnittkrets mot ADCen. Siden LTC6430 har et differensielt utgangsnettverk, kan det drive en differensiell ADC uten en balun, noe som forenkler inngangsnettverket til ADCen ytterligere. Med færre komponenter mellom ADC og forsterker, blir layouten enklere. Man oppnår også et mer balansert nettverk som kan maksimalisere ytelsen til ADCen.

ADC utfordringer

Støy i mottakeren er ikke begrenset bare til forsterker og kanalstøy. Støy på kortet fra offensive signaler kan også koples til ADCens inngangsnettverk og bli digitalisert av ADCen. Mengden av andre støykilder kan reduseres med gode layouteknikker, men noen er uungåelige. En potensiell støykilde i systemet er den digitale utgangen til ADCen. Med store spenningssvingninger og høyt frekvensinnhold, kan de digitale utgangssignalene bli koplet til den analoge inngangen, bli redigitalisert og produsere digital feedback (retur). Digital retur kan produsere lokale topper på opp til 10dB i støygulvet. Singel ende CMOS-signalisering produserer den verste digitale returen, siden jo høyere spenningssvingningene er, jo verre blir den digitale returen.

Digitale linjer forårsaker et mer åpenbart problem: Plassbegrensning. Med begrenset kortplass, vil multikanals ADCer med et stort antall utgangslinjer ta opp verdifull kortplass. Disse bussene med digitale signaler blir fort plagsomme, spesielt når rutingen tar dem nær potensielt følsomme kretser, som referanser, klokker eller inngangsnettverk. Jo nærmere disse digitale bussene er sensitive kretser, jo mer sannsynlig er det at den digitale støyen vil redusere systemets ytelse.

CMOS- og LVDS-spor deler også en annen begrensning: De er ikke DC-balanserte. Det betyr at det ikke er noen mekanisme som opprettholder en gjennomsnittlig DC-verdi. Det faktum at gjennomsnittlig spenning kan flytte seg, betyr at CMOS og LVDS-signaler ikke kan sendes gjennom isolasjonsbarrierer som transformatorer, optiske koplere, DC blokkeringskondensatorer og andre høypasskomponenter.

Antennematriser

I moderne kommunikasjonssystemer, blir antennematriser brukt for romslig mangfold i mottakeren. Dette tillater forbedret signalmottak, spesielt for svake signaler eller signaler utsatt for fading. Imidlertid krever hver tilleggsantenne i matrisen en annen komplett mottakerkjede. Etter hvert som antall antenner øker, er det behov for flere ADC-kanaler. Disse ADCene må synkroniseres for maksimal ytelse, en oppgave som ikke er triviell. Variasjoner i klokkesignalet kan føre til at data blir oversatt feil og redusere systemytelsen. Selv med best mulig spredning av klokkekomponenter kan det fortsatt bli skjevheter mellom de forskjellige klokkebanene som forårsaker skjevheter i digital data. Dette er utfordrende å finne ut av, selv i det digitale området.

ADC-løsninger

Ved å redusere antall datalinjer og bruke digital signalering, reduseres støy introdusert på jordplanet dramatisk. JESD204B-standarden bruker par av CML datalinjer til å sende høyfrekvent seriell data. Avhengig av samplingsraten kreves det så lite som ett linjepar. Disse parene med overføringslinjer er differensielle av natur, så det er en naturlig kansellering av felt som reduserer effekten fra støy koplet til jordplanet. Siden overføringen av data er seriell og 8B/10B-kodet, blir det ikke repetitive mønstre i dataene som kan produsere frekvensinnhold på jordplanet, eller eventuelt dukke opp i den analoge inngangen. Dette reduserer i stor grad sannsynligheten for digital retur i systemet. Med mindre støy og høyt frekvensinnhold på jordplanet, er det mindre energi som kan kople seg til de analog inngangene, noe som reduserer sannsynligheten for digital retur.

Enklere ruting

Ved at data overføres på serielle datapar, blir ruting av disse lederne enklere enn å rute en komplett buss med parallelle data. Siden dataene er overført med kun én eller to par transmisjonslinjer, blir det mye enklere å velge en bane som ikke er omgitt av offensive signaler. Transmisjonslinjeparene kan rutes bort fra sensitive områder på kortet. Et mindre ruteområde tillater også at flere vias kan omgi transmisjonslinjene, noe som igjen reduserer sannsynligheten for at støy vil kople seg til de digitale sporene, eller at støy fra digitale spor vil kople seg til andre sensitive kretser.

DC-balansert

En annen fordel med å bruke 8B/10B-koding er at det er DC-balansert. Det er fordi det eksisterende misforholdet benyttes til å opprettholde likt antall én og null over to alternative kodegrupper, slik at DC gjennomsnitt til signalet er statistisk null. Dette gjør at enkeltpar overføringslinjer kan brukes sammen med transformatorer, optiske koplere, DC blokkeringskondensatorer og andre høypasskomponenter. Ved DC-kopling kan signalet overføres over en isolasjonsbarriere gjennom en transformator eller optisk kopler som vil isolere jordplanet over hele isolasjonsbarrieren. Den sensitive mottakerseksjonen blir elektrisk isolert fra den støyende FPGA-seksjonen, og forbedrer følsomheten til mottakeren ved å redusere støyen på mottakerseksjonen på kortet. Dette tillater at mottakerseksjonen kan være fysisk nær antennen, og ved å bruke en optisk forbindelse for å ha FPGA-seksjonen lengre unna, reduseres støyen koplet fra FPGAen og inn i mottakeren.

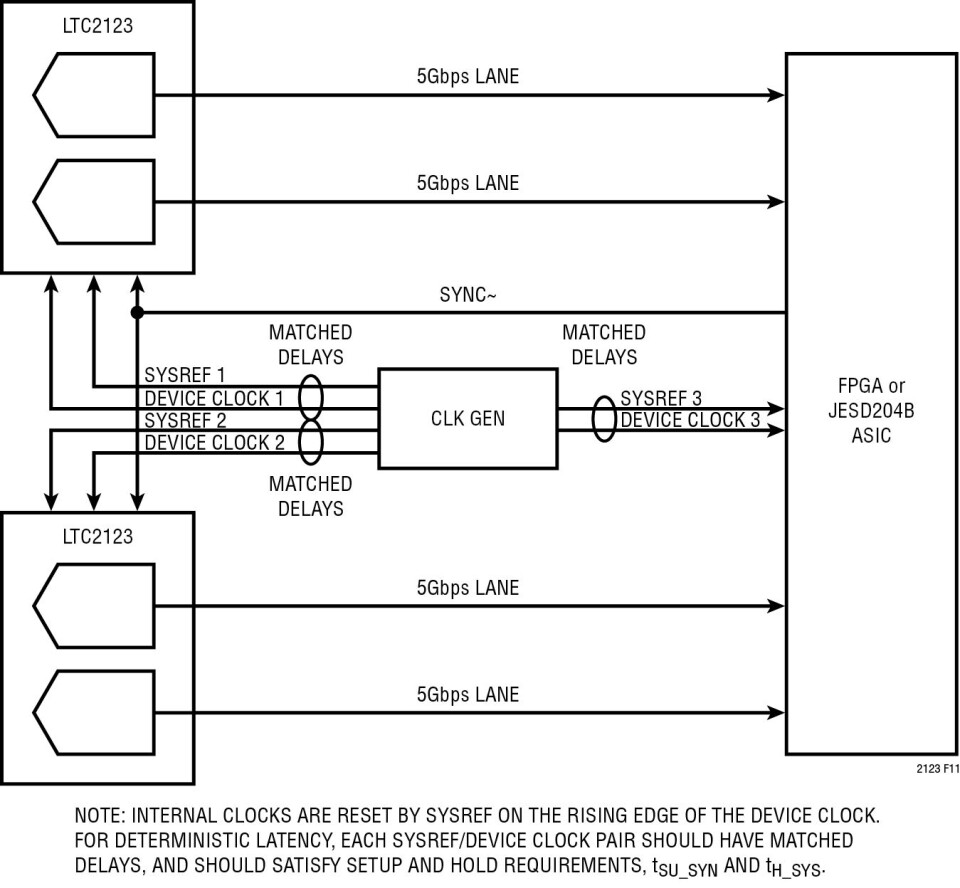

Synkronisering av ADCer

En vesentlig fordel med JESD204B-standarden er muligheten til å synkronisere flere ADCer for å gjøre samtidige samplinger med flere komponenter. Dette er gjort med en klokkestyringskomponent som leverer et SYSREF-signal til hver av ADCene og FPGAen, som vist i figur 1. Når dette SYSREF-signalet er bestemt, vil hver av ADCene og FPGAen justere seg selv til SYSREF-signalet, og data fra hver ADC blir så justert på innsiden av FPGAen. Dette tillater samtidig sampling av flere kanaler med ADC-data fra forskjellige ADCer. Teknikken justerer ADC-data og samplingsklokkene, og gjør synkronisering mye enklere. Med synkroniserte ADCer, er evnen til å motta data fra flere antenner, enkel og triviell, og man kan designe en mer sensitiv mottaker.

Praktisk løsning

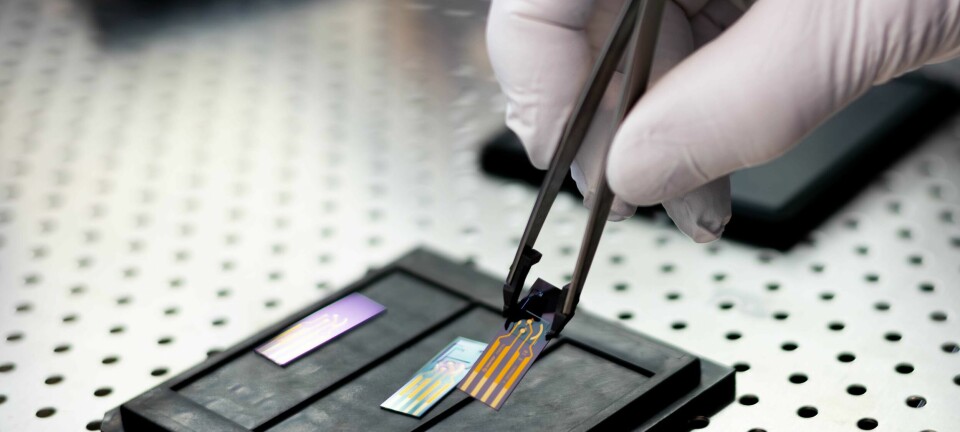

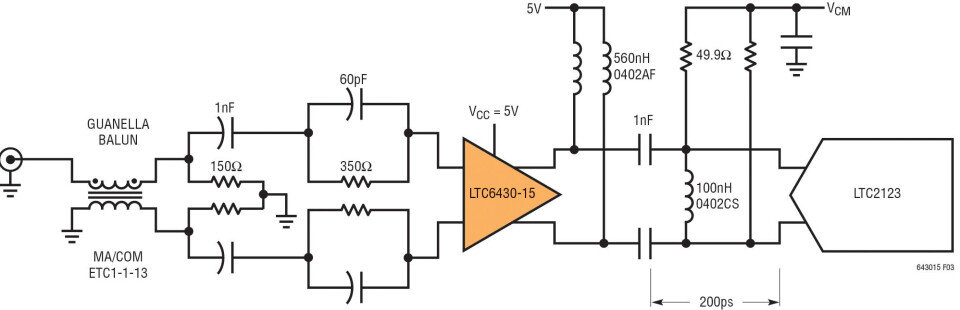

LTC2123 er en dobbel 250Msps 14-bit ADC med JESD204B-grensesnitt. Den har en inngangsbåndbredde på 1250MHz, slik at det kan pares med LTC6430 for å få fram en utmerket undersamplingsmottaker, og er i stand til å motta frekvenser på over 1GHz. Ved å inkludere JESD204B’ens utgangsseksjon, forenkler LTC2123 kortlayout, reduserer støy koplet til jordplanet og gjør at mottakeren blir isolert fra de støyete delene i systemet. Med JESD204B-kretser blir det enklere å synkronisere flere ADCer for å oppnå en stor antennematrise for applikasjoner med antennemangfold. Siden støytallet til LTC6430 er 3dB, kan grensesnittet mellom ADC og forsterker være minimalt.

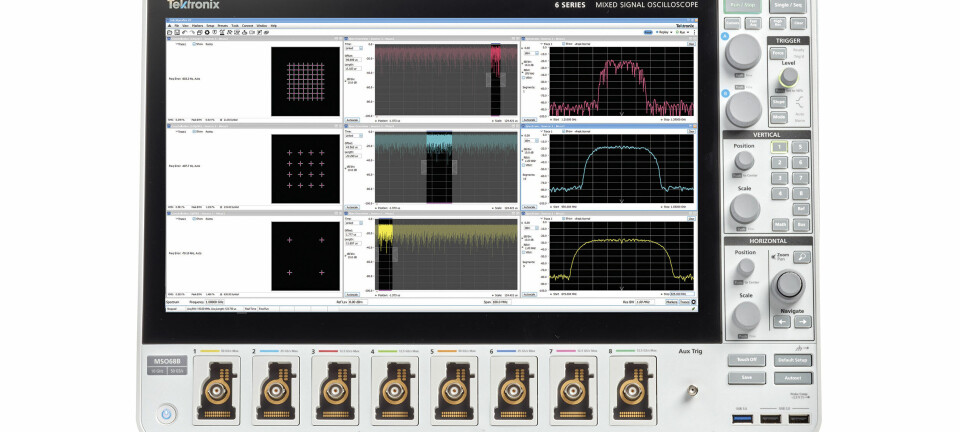

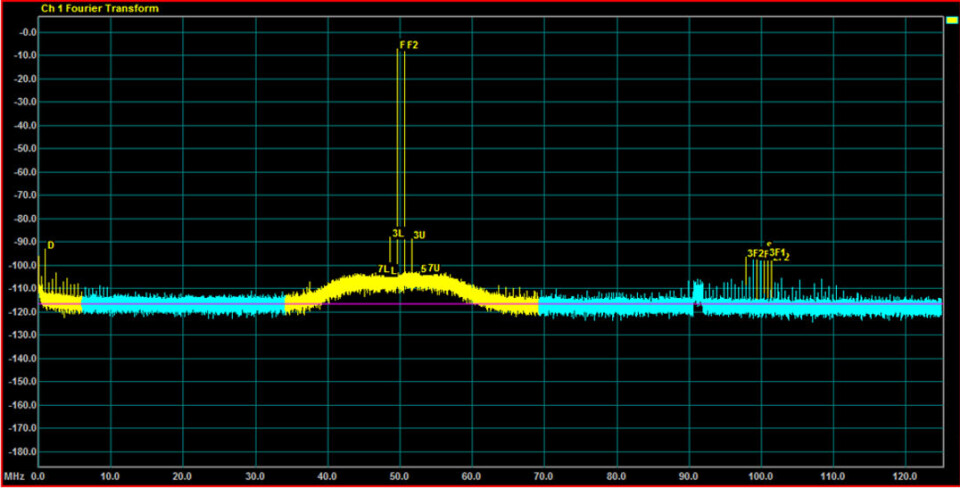

En typisk krets i LTC6430 og LTC2123 er vist i figur 2. Dette tillater at ADC og forsterseksjon kan være kompakt, slik at flere barrierer tillates rundt inngangsnettverket for å redusere støy som kan bli koplet til inngangsnettverket. Resultatet av denne kombinasjonen er vist i figur 3. Ved 250Msps, med toner ved 199,3MHz og 200,3MHz, er forvrengningsproduktene for tredjeordens intermodulasjon på -87dBFS og SNR er 68dBFS. Denne ytelsen er oppnåelig over flere mottakerkanaler i et kompakt område, takket være JESD204B-grensesnittet og det lave energiforbruket til LTC2123 og LTC6430.

Kompakt og stillegående

Kombinasjonen LTC2123 ADC og forsterkeren LTC6430 gjør det mulig å designe kompakte systemer og sikrer maksimal følsomhet i mottakeren. Ved å redusere effekttap og antall digitale linjer kan den totale størrelsen på løsningen reduseres, og barrierer kan etableres rundt følsomme områder i inngangsnettverket. JESD204B-standarden som blir brukt av LTC2123, reduserer støy innført i jordplanet ved å bruke et lite antall overføringslinjepar og lavspent CML signalering. Det gir også en måte å synkronisere flere ADCer på som støtter store antennematriser og antennemangfold.